TI Designs: TIDA-01056

# EMIの最小化と電源効率の最適化を実現する20ビット、1MSPS DAQのリファレンス・デザイン

## TEXAS INSTRUMENTS

## 概要

この高性能データ収集(DAQ)システムのリファレンス・デザインは、電力段を最適化して消費電力を低減し、電磁気干渉(EMI)の影響を最小化します。このデザインはLMS3635-Q1降圧コンバータを使用し、対称形またはバタフライ・レイアウトを活用する HotRod™パッケージにより、高い効率(軽負荷時でも)と非常に低いEMIを実現します。また、

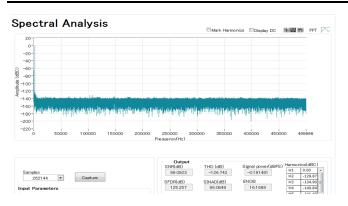

LMS3635-Q1のスイッチング周波数が低いため、設計者は低ドロップアウトのリニア・レギュレータ(LDO)を使用して、出力電圧リップルをより効果的にフィルタリングできます。このリファレンス・デザインは、LM53635降圧コンバータと比較して軽負荷時の効率が7.2%向上しています。スプリアス・フリー・ダイナミック・レンジ(SFDR)は125.25dB、信号対雑音比(SNR)は99dB、有効ビット数(ENOB)は16.1です。

#### リソース

TIDA-01056

デザイン・フォルダ

LMS3635-Q1

プロダクト・フォルダ

TPS7A47

プロダクト・フォルダ

E2Eエキスパートに質問

#### 特長

- DC-DCのEMIがシステム性能に及ぼす影響を最小化する電源設計

- 2つの20ビットSARアナログ/デジタル・コンバータ (ADC)チャネル

- モジュール式のフロントエンド・リファレンス・デザインによる、チャネル数の多いシステム(反復可能)

- 最大±4Vの入力信号(8V<sub>PP</sub>差動)

## アプリケーション

- データ収集(DAQ)

- 半導体試験用機器

- LCD試験用機器

- ラボ計測機器

- バッテリ試験装置

Copyright © 2017, Texas Instruments Incorporate

System Description www.tij.co.jp

使用許可、知的財産、その他免責事項は、最終ページにあるIMPORTANT NOTICE(重要な注意事項)をご参照くださいますようお願いい たします。英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当す る正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては 一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

#### 1 **System Description**

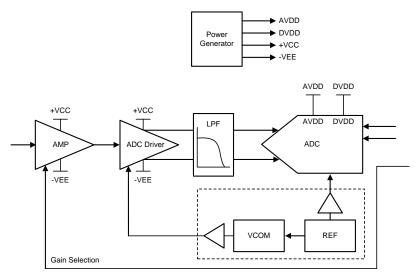

Multi-input systems requiring the simultaneous or parallel sampling of many data channels present design challenges to engineers developing data acquisition (DAQ) modules and automatic testers for applications such as semiconductor tests, memory tests, liquid-crystal display (LCD) tests, and battery tests. In these systems, often hundreds or thousands of data channels are required; thus, maximizing SNR performance while minimizing power, component count, and cost are all key design criteria. These systems have some type of power generator that typically includes DC-to-DC converters to provide the voltage levels required to power each device in the analog front end (AFE). These converters have switching components that cause EMI emission and harm the system performance.

■ 1 shows a block diagram of a generic AFE circuit.

図 1. Generic AFE

#### 1.1 **Key System Specifications**

表 1. Key System Specifications

| PARAMETER           | SPECIFICATIONS                       | MEASUREMENT                          |  |

|---------------------|--------------------------------------|--------------------------------------|--|

| Number of channels  | Dual                                 | Dual                                 |  |

| Input type          | Differential                         | Differential Differential            |  |

| Input range         | 8-V <sub>PP</sub> fully differential | 8-V <sub>PP</sub> fully differential |  |

| Resolution          | 20 bits                              | 20 bits                              |  |

| SNR                 | > 96 dB                              | 99 dB                                |  |

| THD                 | < -120 dB                            | –126.7 dB                            |  |

| ENOB                | > 16 bit                             | 16.16 bits                           |  |

| System power        | < 2.5 W                              | 1.92 W                               |  |

| Form factor (L × W) | 120 mm × 100 mm 112.98 × 99.82 mm    |                                      |  |

## 2 System Overview

## 2.1 Block Diagram

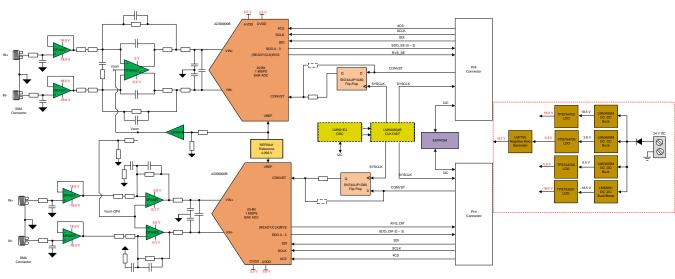

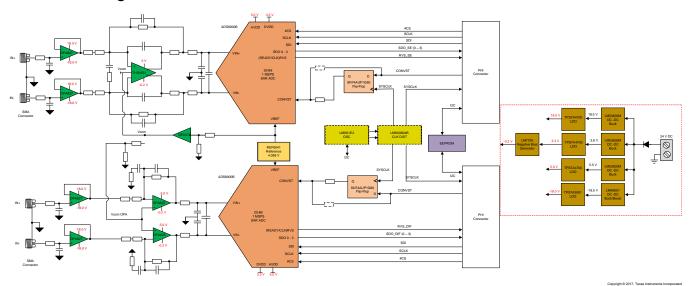

図 2. TIDA-01056 System Block Diagram

This reference design focuses on optimizing power supply efficiency while minimizing the effect of the EMI generated from the system buck converters powering the AFE and 20-bit, 1-MSPS successive approximation register (SAR) ADC. This design compares the efficiency of the LM53635 buck converter, which switches at 2.1 MHz and is used in this reference design, to the LMS3635 buck converter, which has a 400-kHz switching frequency. As both devices use the HotRod™ package and butterfly layout, designers can directly observe the effects of switching frequency on both EMI and efficiency.

## 2.2 Highlighted Products

### 2.2.1 LMS3635-Q1

The function of the LMS3635M in this design is to bring the 24-V input voltage down to 3.8 V, 5.5 V, and 18.5 V in a highly efficient manner. This part is selected based on its superior efficiency at light load, low switching frequency, excellent EMI performance, and compact printed-circuit board (PCB) layout. The automotive-qualified HotRod QFN package reduces parasitic inductance and resistance while increasing efficiency, minimizing switch node ringing, and dramatically lowering EMI. Seamless transition between pulse-width modulation (PWM) and pulse-frequency modulation (PFM) modes, along with a low quiescent current, ensures high efficiency and superior transient responses at all loads.

## 2.2.2 TPS7A47

The TPS7A47 is designed with bipolar technology primarily for high-accuracy, high-precision instrumentation applications where clean voltage rails are critical to maximize system performance. This feature makes the device ideal for powering operational amplifiers, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and other high-performance analog circuitry in critical applications such as medical, radio frequency (RF), and test-and-measurement.

System Overview www.tij.co.jp

## 2.3 System Design Theory

High-performance DAQ systems require low-power consumption while minimizing EMI from switching regulators to prevent from impacting the performance of high-resolution ADCs. The following subsection describes optimizing the power supply stage using the LMS3635-Q1 and provides measurement results and a comparison of the efficiency, SNR, total harmonic distortion (THD), and SFDR.

#### 2.3.1 AFE and SAR ADC

This reference design consists of an AFE with two channels. Both channels are similar, with the exception of the ADC driver architecture. The first channel uses the THS4551, a fully differential amplifier specifically designed to be used with high-performance SAR ADCs. The second channel uses dual OPA625 amplifiers, which are wired to work as a fully differential amplifier. These amplifiers drive the ADS8900B SAR ADC, a 20-bit, high-precision, high-speed data converter. The AFE and SAR ADC are the key aspects of this design for working with DAQ systems; however, these devices are not the main focus of this design. To learn more about the design theory of the AFE and SAR ADC, see *ADC Driver Reference Design Improving Full-Scale THD Using Negative Supply*.

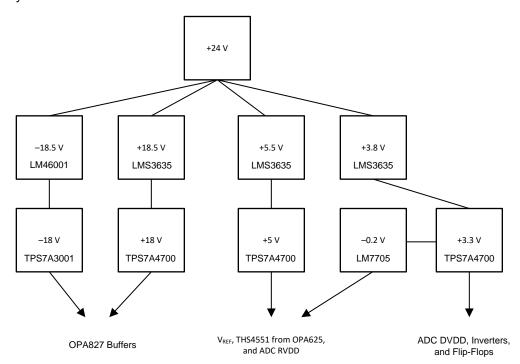

#### 2.3.2 Power Structure

This system requires a wide variety of voltage rails to meet the specification of the reference design. The input voltage required for the system is 24-V DC. The power tree in 3 highlights the distribution of the power into the different required rails. To create these rails, this design contains the LMS3635-Q1 highericiency buck converter. This solution is compared to the LM53635 to show the improvement in efficiency.

図 3. System Power Tree

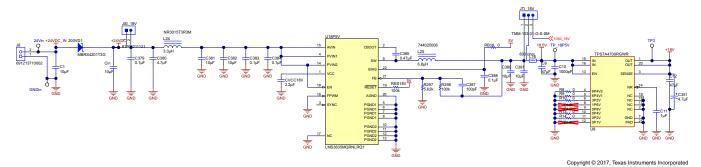

#### 2.3.2.1 LMS3635-Q1 Circuitry

☑ 4 shows the 18-V rail circuitry with the LMS3635-Q1; each rail is structured the same way, with the only difference being the different passive component values. The input of the buck is connected to the 24-V supply by a two-pin header. This header allows the user to leave unused bucks powered off, which is critical to the testing performed on the reference design. The buck converter is followed by an LDO to remove the switching noise. The input of the LDO is connected to a three-pin header. The other two pins of this header are connected to the outputs of both buck converter options. This header is used in conjunction with the two-pin header to properly connect the buck, for which the intention is to use with the LDO. The three-pin header allows the use of only one LDO for each rail, which improves space efficiency and also helps with certain aspects of testing and debugging.

図 4. LMS3635-Q1 Schematic

#### 2.3.3 LMS3635-Q1 Switching Noise

Buck converters produce output voltage ripple, which is also known as switching noise. Many different factors involving the switching regulator determine the amplitude of this ripple, which can be high enough to cause issues with devices powered by this buck converter. Because this reference design uses noise-sensitive devices such as the 20-bit ADC, a high-voltage ripple can have a detrimental effect on signal integrity. An LDO is placed at the output of the switching regulator to remove the switching noise and circumvent such an occurrence.

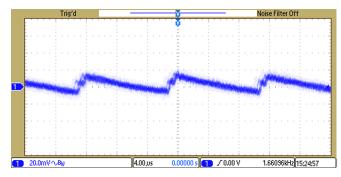

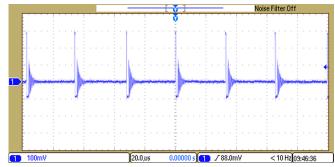

The following calculations and simulations show the importance of connecting the LDO to remove the switching frequency. The output voltage ripple and switching frequency ( $f_s$ ) for the buck in the 5-V rail (the rail powering the RVDD of the ADC,  $V_{REF}$ , OPA625, and THS4551) was measured to be approximately 30 mV and 30 kHz (see  $\boxtimes$  5 and  $\boxtimes$  6, respectively).

☑ 5. Output Ripple of LMS3635-Q1 (5-V Rail)

図 6. Switching Waveform of LMS3635-Q1 (5-V Rail)

System Overview www.tij.co.jp

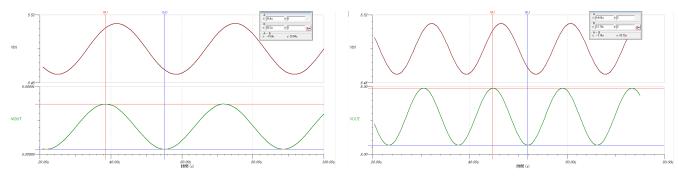

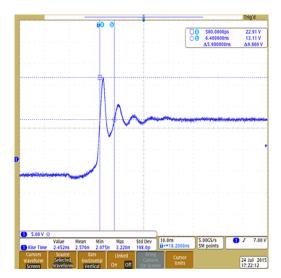

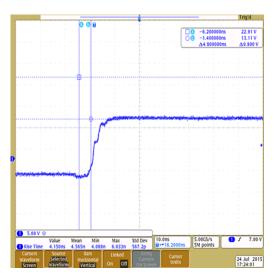

The buck is designed to output 5.5 V, which is just above the dropout of the LDO, to minimize the efficiency loss. A TINA-TI<sup>TM</sup> simulation model is created for the TPS7A4700 LDO with a 5.5-V DC level and a sine wave input of 30 mV<sub>pk-pk</sub>, 30 kHz (simulating the output of the LMS3635 device with ripple). A steady-state analysis provided the output of the LDO, which  $\boxtimes$  7 shows.

As for the LM53635—because the output current of the 5.5-V rail is measured as 20 mA—its switching frequency must be around 70 kHz, as evidenced from the *Switching Frequency vs Load Current* graph in *LM53625/35-Q1, 2.5-A or 3.5-A, 36-V Synchronous, 2.1-MHz, Step-Down DC-DC Converter.* 🗵 8 shows the LDO simulation result, which was obtained under the same DC level and amplitude as the LMS3635 device.

図 8. LDO Simulation V<sub>IN</sub> from LM53635 for 5-V Rail

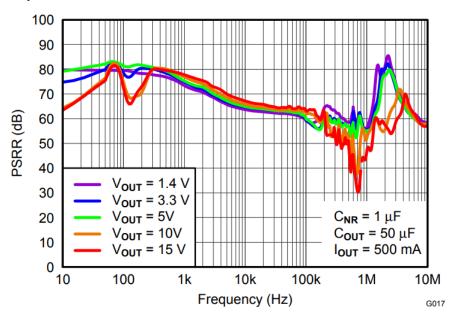

After the LDO, the peak-to-peak switching noise of the LMS3635-Q1 and LM53635 are 20.04  $\mu$ V and 33.72  $\mu$ V, respectively. Because the LDO has an improved power supply rejection ratio (PSRR) at lower frequencies (see  $\boxtimes$  9), the ripple rejection of the LMS3635-Q1 (30-kHz switching) is 41% superior to the LM53635 (70-kHz switching). Thus, from a ripple and EMI perspective, the LMS3635-Q1 is more suitable for high-accuracy DAQ.

図 9. PSRR of TPS7A47x

The LDO effectively reduces the switching ripple noise by a factor of 1497. Further calculations are made to observe the noise present at the ADC using the output voltage ripple of the LMS3635-Q1 device. Compare this result to the result of using the output voltage ripple of the TPS7A4700 in the same calculations. This ripple voltage without the LDO goes to both the OPA625 and THS4551 devices. The THS4551 has a PSRR of 110 dB at 30 kHz and a gain of 1. 式 1 shows that the PSRR is equal to:

$$PSSR(dB) = -20log_{10} \left( \frac{\Delta V_{OS}}{\Delta V_{SUPPLY}} \right)$$

(1)

Because this system has a gain of 1, the total noise gain on the non-inverting terminal is 1 + 1. This is a gain of 6 dB. The total PSRR for the THS4551 is approximately 104 dB for this system. This value is equal to 0.00000631 V/V. The amount of power supply noise coupled to the ADC data lines is calculated using  $\frac{1}{2}$ :

$$30 \text{ mV} \times 0.00000631 = 189.3 \text{ nV}$$

(2)

Compare this noise value to the least significant bit (LSB) value of the ADC to observe the effect it has on signal integrity. Calculate the value of 1 LSB for a 20-bit differential input ADC with 4.096 V as a reference voltage using 式 3 and 式 4:

$$\frac{2 \times 4.096}{2^{20}} = 7.812 \,\mu\text{V} \tag{3}$$

$$\frac{189.3 \,\text{nV}}{7.812 \,\mu\text{V}} \times 100 = 2.42\% \,\text{LSB} \tag{4}$$

Because the ADS8900B has a differential input, the full-scale input range (FSR) is twice the reference voltage. To determine the LSB of the differential input ADC, see the section regarding the *ADC Transfer Function* in *ADS890xB 20-Bit*, *High-Speed SAR ADCs With Integrated Reference Buffer, and Enhanced Performance Features*. The OPA625 has a power supply rejection ratio of 77 dB at 30 kHz. At a gain of 1, the PSRR is equal to 71 dB. This value is equivalent to 0.00028 V/V. 式 5 and 式 6 calculate the power supply noise present at the ADC driven by the OPA625 device:

$$30 \text{ mV} \times 0.00028 = 8.46 \,\mu\text{V}$$

(5)

$$\frac{8.46\,\mu\text{V}}{7.812\,\mu\text{V}} \times 100 = 108\% \,\text{LSB} \tag{6}$$

With a 2.42% LSB present at the ADC, the THS4551 signal chain is not greatly impacted by excluding the LDO. However, the OPA625 signal chain has more than 1 LSB of power supply noise present at the ADC without the LDO. This above 1 LSB noise value causes missing code and creates a huge negative impact on the output data of the ADC. Using the LDO output ripple of 20.04  $\mu$ V and the same equations, the amount of power supply noise coupled to the ADC data lines for the ADC driven by the THS4551 is:

$$20.04 \,\mu\text{V} \times 0.00000631 = 126.4 \,\text{pV}$$

(7)

$$\frac{126.4 \,\mathrm{pV}}{7.812 \,\mu\mathrm{V}} \times 100 = 0.0016\% \,\mathrm{LSB} \tag{8}$$

This highlights that the amount of noise on the 5-V rail is much less than 1% of the LSB value of the ADC. The amount of power supply noise present at the ADC of the OPA625 is:

$$20.04 \,\mu\text{V} \times 0.00028 = 5.65 \,\text{nV}$$

(9)

ス・デザイン

System Overview www.tij.co.jp

$$\frac{5.65\,\mathrm{nV}}{7.812\,\mu\mathrm{V}}\times\,100 = 0.072\%\,LSB$$

(10)

When using the LDO, both the THS4551 and OPA625 signal chain ADCs have much less than 1% LSB of noise present at their power supply inputs. This specification ensures that there is no negative impact on signal integrity with the LDO present in the system. This test concludes that the LDO is necessary in the power rail circuits to generally remove any system performance degradation as a result of switching noise.

#### 2.3.4 LMS3635-Q1 EMI

One of the goals for this design is to eliminate any system performance degradation due to EMI for high-performance DAQ systems. Buck converters are the main source of unwanted spur production throughout the spectrum due to their harsh switching components. The LMS3635-Q1 is a great solution for this problem because many of its features focus on reducing EMI.

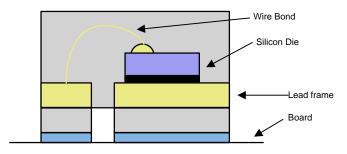

## 2.3.4.1 HotRod™ Packaging

The biggest factor that helps the LMS3635-Q1 reduce EMI is the HotRod Flip-Chip-on-Leadframe (FCOL) packaging, which ☑ 11 shows. This package style flips the die over and uses copper bumps to connect directly to the leads, thus eliminating the requirement for a wire bond (see ☑ 10). Removing this wire bond reduces the parasitics, which dramatically lowers the switch node ringing. This ringing is a major source of EMI for buck converters using the standard wire-bond packaging.

Silicon Die

Copper bump

Solder

Lead frame

Board

図 10. Standard Wire-Bond QFN

図 11. HotRod™ FCOL QFN

$\boxtimes$  12 and  $\boxtimes$  13 show the difference between switch node ringing for a wire-bond package and a HotRod package. The ringing overshoot reduces from 9 V to 0 V, which lowers the overall EMI and noise. The HotRod packaging helps to reduce EMI and allows for a smaller size and reduced R<sub>DS\_ON</sub>, which improves the efficiency.

図 12. LM53603 TSSOP

図 13. LM53635-Q1 FCOL

## 3 Hardware, Software, Testing Requirements, and Test Results

## 3.1 Required Hardware

This section outlines the information for getting the board up and running quickly. To learn about the precision host interface (PHI) board or the onboard clocking and jitter cleaner, see *Optimized Analog Front-End DAQ System Reference Design for 18-Bit SAR Data Converters*. Take care when moving jumper pins to avoid possible damage to the components.

#### 3.1.1 Jumper Configuration

This system has several configurable power options. These options are selectable through using two-pin and three-pin jumpers. 表 2 highlights the purpose of each jumper and assists in changing the configuration to fit the user requirements.

表 2. Jumper Configuration

| JUMPER NAME | SHORT PINS 1 AND 2                               | SHORT PINS 2 AND 3                              | DEFAULT CONFIGURATION |  |

|-------------|--------------------------------------------------|-------------------------------------------------|-----------------------|--|

| JSI_18V     | Power to LMS3635-Q1 18-V rail                    | _                                               | Short                 |  |

| JTI_18V     | Connects LMS3635-Q1 to<br>TPS7A700 for 18-V rail | Connects LMZ14201 to<br>TPS7A700 for 18-V rail  | Short pins 1 and 2    |  |

| JSI_5V      | Power to LMS3635-Q1 5-V rail                     | _                                               | Short                 |  |

| JTI_5V      | Connects LMS3635-Q1 to<br>TPS7A700 for 5-V rail  | Connects LMZ14203 to<br>TPS7A700 for 5-V rail   | Short pins 1 and 2    |  |

| JSI_3.3V    | Power to LMS3635-Q1 3.3-V rail                   | _                                               | Short                 |  |

| JTI_3.3V    | Connects LMS3635-Q1 to TPS7A700 for 3.3-V rail   | Connects LMZ14202 to<br>TPS7A700 for 3.3-V rail | Short pins 1 and 2    |  |

| JPRI18V     | Power to LM46001 –18-V rail                      | _                                               | Short                 |  |

| JTI18V      | Connects LM46001 to TPS7A3001 for -18-V rail     | Connects LM5574 to TPS7A3001 for –18-V rail     | Short pins 1 and 2    |  |

| JMTI18V     | Power to LM5574 –18-V rail                       | _                                               | Open                  |  |

| JZI_18V     | Power to LMZ14201 18-V rail                      | _                                               | Open                  |  |

| JZI_3.3V    | Power to LMZ14202 3.3-V rail                     | _                                               | Open                  |  |

| JZI_5V      | Power to LMZ14203 5-V rail                       |                                                 | Open                  |  |

| J39         | Connects –0.2-V rail to OPA625<br>and THS4551    | Shorts –0.2-V rail to ground Short pins 1 and 2 |                       |  |

## 3.2 Testing and Results

### 3.2.1 Efficiency

The efficiency of each buck converter (3.8 V, 5.5 V, and 18.5 V) was evaluated with those devices implemented on the system board. Because the LMS3635-Q1 is capable of superior light load mode, it has an overall better efficiency than the LM53635. Specifically, at a 15.7-mA output current (see  $\pm$  3), the efficiency improved by 7.2% (89/83-1).

| VOLTAGE<br>SOURCE | OUTPUT<br>VOLTAGE (V) | OUTPUT<br>CURRENT (mA) | INPUT<br>VOLTAGE (V) | INPUT<br>CURRENT (mA) | EFFICIENCY (%) |

|-------------------|-----------------------|------------------------|----------------------|-----------------------|----------------|

| LMS3635-Q1        | 3.804                 | 184                    | 24                   | 33                    | 88             |

|                   | 5.488                 | 20.1                   | 24                   | 5.26                  | 87             |

|                   | 19.077                | 15.7                   | 24                   | 14                    | 89             |

| LM53635-Q1        | 3.813                 | 184                    | 24                   | 34                    | 86             |

|                   | 5.492                 | 20.1                   | 24                   | 5.26                  | 87             |

|                   | 19.093                | 15.7                   | 24                   | 15                    | 83             |

表 3. Efficiency Evaluation Results

#### 3.2.2 EMI Matters

An Audio Precision 2700 series signal generator is used as the signal source to test the AFE and ADC performance. The noise and THD of the AP2700 have adequate performance and do not limit measurements or system performance. A generic DC power supply is used to generate the 24-V DC input voltage.

A PHI controller board is used to connect the TIDA-01056 board to the host PC, where the ADS8900B EVM GUI functions. This software allows the designer to measure SNR, THD, SFDR, signal-to-noise and distortion ratio (SINAD), and ENOB for the ADC by running a spectral analysis. The AP2700 is set to output a 2-kHz 8- $V_{pk-pk}$  sinusoid. A value of 2 kHz is chosen because it is the standard frequency when measuring noise and THD, and 8- $V_{pk-pk}$  grants full range on the THS4551 or OPA625 devices, thus granting a full range of 0 to the  $V_{REF}$  for the ADC.

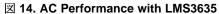

AC performance was measured for both the LMS3635-Q1 and LM53635-Q1 devices (see 🗵 14 and 🗵 15). The LMS3635 slightly outperformed the LM53635 by almost 1 dB in SFDR. According to *Multi-Rail Power Reference Design for Eliminating EMI Effects in High-Performance DAQ Systems*, the LM53635 gives a comparable performance to the same system with external power supplies. Thus, the LMS3635 device can reduce power consumption and reduce voltage ripple while minimizing the effect of EMI from switching noise.

図 15. AC Performance with LM53635

www.tij.co.jp Design Files

## 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01056.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01056.

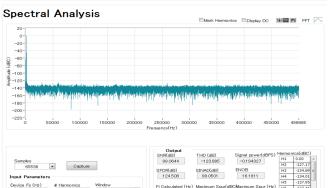

## 4.3 PCB Layout Recommendations

The LMS3635-Q1 has certain layout guidelines that help to reduce EMI. ☑ 16 shows how the LMS3635-Q1 and its additional components must be placed in the layout.

図 16. LMS3635-Q1 Layout Guidelines

Putting the input and output capacitors in this configuration creates parallel capacitance loops, thus minimizing the inductance. This placement then reduces the switch node ringing and lowers the overall EMI emissions. TI also recommends leaving the ground plane unbroken under the device. This placement provides the shortest return path possible, minimizing EMI generated by the loop. For more layout recommendations regarding the AFE or SAR ADC, see *Optimized Analog Front-End DAQ System Reference Design for 18-Bit SAR Data Converters*.

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01056.

## 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01056.

Design Files www.tij.co.jp

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01056.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01056.

#### 5 Software Files

To download the software files, see the design files at TIDA-01056.

#### 6 Related Documentation

- 1. Texas Instruments, ADC Driver Reference Design Improving Full-Scale THD Using Negative Supply

- 2. Texas Instruments, ADS890xB 20-Bit, High-Speed SAR ADCs With Integrated Reference Buffer, and Enhanced Performance Features

- 3. Texas Instruments, Multi-Rail Power Reference Design for Eliminating EMI Effects in High-Performance DAQ Systems

- 4. Texas Instruments, Optimized Analog Front-End DAQ System Reference Design for 18-Bit SAR Data Converters

#### 6.1 商標

HotRod, TINA-TI are trademarks of Texas Instruments. すべての商標および登録商標はそれぞれの所有者に帰属します。

#### 7 About the Authors

**SHOTA MAGO** is a field application engineer at Texas Instruments, where he is responsible for supporting Japanese industrial companies and proposing solutions for them. Shota obtained his bachelor's degree and master of electrical and electronic engineering from the University of Miyazaki in Japan.

**TARAS DUDAR** is a systems design engineer and architect at Texas Instruments, where he is responsible for developing reference design solutions for the test and measurement industry. Previously, Taras designed high-speed analog SOC integrated circuits for Gbps data communications. Taras earned his master of science in electrical engineering (MSEE) degree from the Oregon State University in Corvallis, OR.

#### TIの設計情報およびリソースに関する重要な注意事項

Texas Instruments Incorporated ("TI")の技術、アプリケーションその他設計に関する助言、サービスまたは情報は、TI製品を組み込んだアプリケーションを開発する設計者に役立つことを目的として提供するものです。これにはリファレンス設計や、評価モジュールに関係する資料が含まれますが、これらに限られません。以下、これらを総称して「TIリソース」と呼びます。いかなる方法であっても、TIリソースのいずれかをダウンロード、アクセス、または使用した場合、お客様(個人、または会社を代表している場合にはお客様の会社)は、これらのリソースをここに記載された目的にのみ使用し、この注意事項の条項に従うことに合意したものとします。

TIによるTIリソースの提供は、TI製品に対する該当の発行済み保証事項または免責事項を拡張またはいかなる形でも変更するものではなく、これらのTIリソースを提供することによって、TIにはいかなる追加義務も責任も発生しないものとします。TIは、自社のTIリソースに訂正、拡張、改良、およびその他の変更を加える権利を留保します。

お客様は、自らのアプリケーションの設計において、ご自身が独自に分析、評価、判断を行う責任がお客様にあり、お客様のアプリケーション(および、お客様のアプリケーションに使用されるすべてのTI製品)の安全性、および該当するすべての規制、法、その他適用される要件への遵守を保証するすべての責任をお客様のみが負うことを理解し、合意するものとします。お客様は、自身のアプリケーションに関して、(1) 故障による危険な結果を予測し、(2) 障害とその結果を監視し、および、(3) 損害を引き起こす障害の可能性を減らし、適切な対策を行う目的での、安全策を開発し実装するために必要な、すべての技術を保持していることを表明するものとします。お客様は、TI製品を含むアプリケーションを使用または配布する前に、それらのアプリケーション、およびアプリケーションに使用されているTI製品の機能性を完全にテストすることに合意するものとします。TIは、特定のTIリソース用に発行されたドキュメントで明示的に記載されているもの以外のテストを実行していません。

お客様は、個別のTIリソースにつき、当該TIリソースに記載されているTI製品を含むアプリケーションの開発に関連する目的でのみ、使用、コピー、変更することが許可されています。明示的または黙示的を問わず、禁反言の法理その他どのような理由でも、他のTIの知的所有権に対するその他のライセンスは付与されません。また、TIまたは他のいかなる第三者のテクノロジまたは知的所有権についても、いかなるライセンスも付与されるものではありません。付与されないものには、TI製品またはサービスが使用される組み合わせ、機械、プロセスに関連する特許権、著作権、回路配置利用権、その他の知的所有権が含まれますが、これらに限られません。第三者の製品やサービスに関する、またはそれらを参照する情報は、そのような製品またはサービスを利用するライセンスを構成するものではなく、それらに対する関係証または推奨を意味するものでもありません。TIリソースを使用するため、第三者の特許または他の知的所有権に基づく第三者からのライセンス、もしくは、TIの特許または他の知的所有権に基づくTIからのライセンスが必要な場合があります。

TIのリソースは、それに含まれるあらゆる欠陥も含めて、「現状のまま」提供されます。TIは、TIリソースまたはその仕様に関して、明示 的か暗黙的かにかかわらず、他のいかなる保証または表明も行いません。これには、正確性または完全性、権原、続発性の障害に関する保 証、および商品性、特定目的への適合性、第三者の知的所有権の非侵害に対する黙示の保証が含まれますが、これらに限られません。

TIは、いかなる苦情に対しても、お客様への弁護または補償を行う義務はなく、行わないものとします。これには、任意の製品の組み合わせに関連する、またはそれらに基づく侵害の請求も含まれますが、これらに限られず、またその事実についてTIリソースまたは他の場所に記載されているか否かを問わないものとします。いかなる場合も、TIリソースまたはその使用に関連して、またはそれらにより発生した、実際的、直接的、特別、付随的、間接的、懲罰的、偶発的、または、結果的な損害について、そのような損害の可能性についてTIが知らされていたかどうかにかかわらず、TIは責任を負わないものとします。

お客様は、この注意事項の条件および条項に従わなかったために発生した、いかなる損害、コスト、損失、責任からも、TIおよびその代表者を完全に免責するものとします。

この注意事項はTIリソースに適用されます。特定の種類の資料、TI製品、およびサービスの使用および購入については、追加条項が適用されます。これには、半導体製品(http://www.ti.com/sc/docs/stdterms.htm)、評価モジュール、およびサンプル(http://www.ti.com/sc/docs/sampterms.htm)についてのTIの標準条項が含まれますが、これらに限られません。

Copyright © 2018, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社