**TLV1872** JAJSRI6 - MARCH 2024

# TLV1871/2 入力電源と出力電源が独立した 40V 高速コンパレータ

## 1 特長

- 幅広い電源電圧範囲:2.7V~40V(±1.35V~±20V)

- 単一電源または分割電源動作

- 個別電源で「フローティング」プッシュプル出力

- 出力電源により、最大出力スイングが設定されます。

- レールツーレール入力

- パワーオン リセット (POR)

- 伝搬遅延時間:65ns

- 低い入力オフセット電圧:500µV

- 低い消費電流:70µA (チャネルあたり)

- 温度範囲:-40℃~+125℃

## 2 アプリケーション

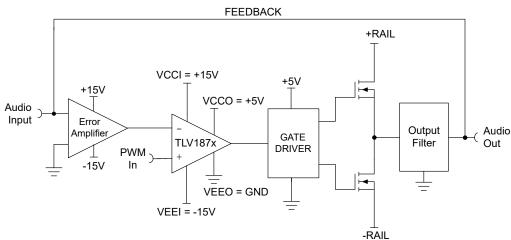

- クラス D アンプ

- レベルトランスレータ

- モータードライブ

- バイポーラ ゼロ クロス検出器

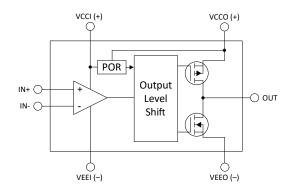

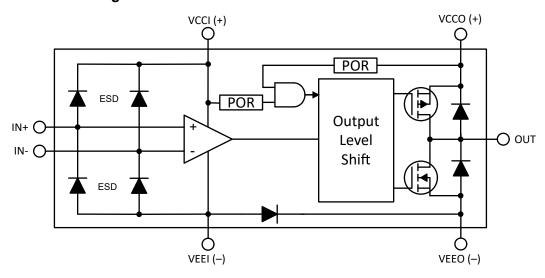

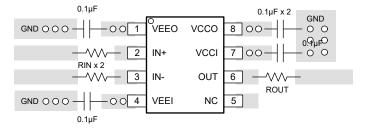

## 概略内部図

## 3 概要

TLV187x は、レール ツー レール入力、プッシュプル出力 段を備えた 40V 高速コンパレータです。TLV187x には、 独立した入力電源と出力電源によるレベルシフト機能もあ ります。これらの特長と 65ns の伝搬遅延の組み合わせに より、このファミリはバイポーラのゼロクロス検出、クラス **D** オーディオ アンプ システム、またはレベル変換と伝搬遅 延の対称性を必要とするその他のアプリケーションに最適 です。

このデバイスは、パワーオン リセット (POR) 機能を搭載し ており、電源電圧が最小値に達するまでの間、出力が入 力に応答する前に、出力が既知の状態であることが保証 されるため、システムの電源オンおよび電源オフ時に誤っ た出力が発生されるのを防止できます。

TLV187x にはプッシュプル出力段があるため、立ち上が りと立ち下がりの出力応答に対称性が求められるアプリケ ーションに最適です。このデバイスは、入力電源と出力電 源が独立しているため、より低い電圧の下流デバイスに対 するレベル変換が可能です。

## 製品情報

| 部品番号          | パッケージ <sup>(1)</sup> | 本体サイズ (公称)(2)   |

|---------------|----------------------|-----------------|

| TLV1871 (プレビュ | SOT-23 (8)           | 1.60mm × 2.90mm |

| —)            |                      |                 |

| TLV1872       | VSSOP (10)           | 3.00mm × 3.00mm |

- 利用可能なすべてのパッケージについては、データシートの末尾 (1) にある注文情報を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

クラス D アンプの例

## **Table of Contents**

| 1 特長                                   | 1 | 6.3 Feature Description              | 15               |

|----------------------------------------|---|--------------------------------------|------------------|

| 2 アプリケーション                             |   | 6.4 Device Functional Modes          |                  |

| 3 概要                                   | _ | Application and Implementation       | 19               |

| 4 Pin Configuration and Functions      |   | 7.1 Application Information          | 19               |

| 4.1 Pin Configurations: TLV1871 Single |   | 7.2 Typical Applications             | <mark>2</mark> 1 |

| Pin Configurations: TLV1872 Dual       |   | 7.3 Power Supply Recommendations     | <mark>22</mark>  |

| 5 Specifications                       |   | 7.4 Layout                           | 22               |

| 5.1 Absolute Maximum Ratings           |   | Device and Documentation Support     | <mark>2</mark> 3 |

| 5.2 ESD Ratings                        |   | 8.1 Documentation Support            | 23               |

| 5.3 Thermal Information.               |   | 8.2ドキュメントの更新通知を受け取る方法                | 23               |

| 5.4 Recommended Operating Conditions   |   | 8.3 サポート・リソース                        | 23               |

| 5.5 Electrical Characteristics         |   | 8.4 Trademarks                       |                  |

| 5.6 Switching Characteristics          |   | 8.5 静電気放電に関する注意事項                    |                  |

| 5.7 Typical Characteristics            |   | 8.6 用語集                              |                  |

| 6 Detailed Description                 |   | Revision History                     |                  |

| 6.1 Overview                           |   | Mechanical, Packaging, and Orderable |                  |

| 6.2 Functional Block Diagram           |   | Information                          | 24               |

| •                                      |   |                                      |                  |

# **4 Pin Configuration and Functions**

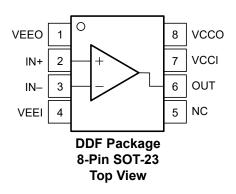

# 4.1 Pin Configurations: TLV1871 Single

表 4-1. Pin Functions

| PIN  |     |     | DECODINE                       |

|------|-----|-----|--------------------------------|

| NAME | NO. | I/O | DESCRIPTION                    |

| VEEO | 1   | _   | Output negative supply voltage |

| IN+  | 2   | I   | Non-Inverting input            |

| IN-  | 3   | I   | Inverting input                |

| VEEI | 4   | _   | Input negative supply voltage  |

| NC   | 5   | _   | No connect                     |

| OUT  | 6   | 0   | Output                         |

| VCCI | 7   | _   | Input positive supply voltage  |

| VCCO | 8   | _   | Output positive supply voltage |

3

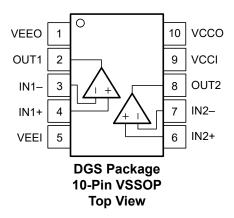

# Pin Configurations: TLV1872 Dual

表 4-2. Pin Functions

| PIN  |     | 1/0 | DESCRIPTION                             |

|------|-----|-----|-----------------------------------------|

| NAME | NO. | I/O | DESCRIPTION                             |

| VEEO | 1   | _   | Output negative supply voltage          |

| OUT1 | 2   | 0   | Output pin of the comparator 1          |

| IN1- | 3   | I   | Inverting input pin of comparator 1     |

| IN1+ | 4   | I   | Non-Inverting input pin of comparator 1 |

| VEEI | 5   | _   | Input negative supply voltage           |

| IN2+ | 6   | I   | Non-Inverting input pin of comparator 2 |

| IN2- | 7   | I   | Inverting input pin of comparator 2     |

| OUT2 | 8   | 0   | Output pin of the comparator 2          |

| VCCI | 9   | _   | Input positive supply voltage           |

| VCCO | 10  | _   | Output positive supply voltage          |

Copyright © 2024 Texas Instruments Incorporated

## **5 Specifications**

### 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                              | MIN                    | MAX                       | UNIT |

|--------------------------------------------------------------|------------------------|---------------------------|------|

| Input Supply Voltage: (V <sub>CCI</sub> – V <sub>EEI</sub> ) | -0.3                   | 42                        | V    |

| Output Negative Supply Voltage: V <sub>EEO</sub>             | V <sub>EEI</sub>       | V <sub>EEI</sub> + 20     | V    |

| Output Positive Supply Voltage: V <sub>CCO</sub>             | V <sub>EEO</sub> - 0.3 | V <sub>CCI</sub> + 0.3    | V    |

| Input pins (IN+, IN-) (2)                                    | V <sub>EEI</sub> - 0.3 | V <sub>CCI</sub> + 0.3    | V    |

| Current into input pins (IN+, IN-) (2)                       | -10                    | 10                        | mA   |

| Output (OUT) from V <sub>EEO</sub> (3)                       | -0.3                   | (V <sub>CCO</sub> ) + 0.3 | V    |

| Output short circuit current <sup>(4) (5)</sup>              | -10                    | 10                        | mA   |

| Junction temperature, T <sub>J</sub>                         |                        | 150                       | °C   |

| Storage temperature, T <sub>stg</sub>                        | -65                    | 150                       | °C   |

- (1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) Input terminals are diode-clamped to (V<sub>EEI</sub>) and (V<sub>CCI</sub>). Input signals that can swing more than 0.3 V beyond the supply rails must be current-limited to 10 mA or less.

- (3) Output (OUT) is diode-clamped to (V<sub>EEO</sub>) and (V<sub>CCO</sub>). Please see the Outputs and ESD Protection section of the Application Information Section for more information.

- (4) Output sinking and sourcing current is internally limited to <35mA when operating within the Absolute Maximum output voltage limits. The Absolute Maximum Output Current limit specified here is the maximum current through the clamp structure when exceeding the supply votlage below (V<sub>FFO</sub>) or above (V<sub>CCO</sub>).

- (5) Continuous output short circuits at elevated supply voltages can result in excessive heating and exceeding the maximum allowed junction temperature, leading to eventual device destruction.

## 5.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | v    |

- (1) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

5

English Data Sheet: SNOSDI4

## 5.3 Thermal Information

|                       |                                              | TLV1871 | TLV1872 |      |

|-----------------------|----------------------------------------------|---------|---------|------|

|                       | THERMAL METRIC(1)                            |         |         | UNIT |

|                       |                                              | 8 PINS  | 8 PINS  |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | _       | 151.4   | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | _       | 55.0    | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | _       | 84.9    | °C/W |

| ΨЈΤ                   | Junction-to-top characterization parameter   | -       | 3.2     | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | -       | 83.7    | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | -       | _       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics report.

## **5.4 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                                           | MIN                    | MAX                    | UNIT |

|-----------------------------------------------------------|------------------------|------------------------|------|

| Input Supply Voltage: V <sub>CCI</sub> – V <sub>EEI</sub> | 2.7                    | 40                     | V    |

| Output Negative Supply Voltage: V <sub>EEO</sub>          | V <sub>EEI</sub>       | V <sub>EEI</sub> + 18  | V    |

| Output Positive Supply Voltage: V <sub>CCO</sub>          | V <sub>EEO</sub> + 2.7 | V <sub>CCI</sub>       | V    |

| Input voltage range from V <sub>EEI</sub>                 | - 0.2                  | V <sub>CCI</sub> + 0.2 | V    |

| Ambient temperature, T <sub>A</sub>                       | -40                    | 125                    | °C   |

## **5.5 Electrical Characteristics**

For VCCI = 12 V, VEEI = 0 V, VCCO = 3.3 V, VEEO = 0 V, V<sub>CM</sub> = 0 V at T<sub>A</sub> = 25°C (Unless otherwise noted)

| P                     | ARAMETER                               | TEST CONDITIONS                                                                         | MIN                    | TYP  | MAX                    | UNIT  |

|-----------------------|----------------------------------------|-----------------------------------------------------------------------------------------|------------------------|------|------------------------|-------|

| OFFSET V              | OLTAGE                                 |                                                                                         |                        |      |                        |       |

|                       | Input offset                           | T <sub>A</sub> = 25°C                                                                   | -4.5                   | ±0.5 | 4.5                    | mV    |

| V <sub>OS</sub>       | V-00                                   | T <sub>A</sub> = -40°C to +125°C                                                        | -5                     |      | 5                      | mV    |

| dV <sub>IO</sub> /dT  | Input offset voltage drift             | T <sub>A</sub> = -40°C to +125°C                                                        |                        | ±1.2 |                        | μV/°C |

| POWER SI              | UPPLY                                  |                                                                                         |                        |      |                        |       |

|                       |                                        | No Load, Output High T <sub>A</sub> = 25°C                                              |                        | 70   | 85                     | μA    |

|                       | Quiescent current                      | No Load, Output High T <sub>A</sub> = -40°C to +125°C                                   |                        |      | 90                     | μΑ    |

| IQ                    | per comparator (2)                     | No Load, Output Low<br>T <sub>A</sub> = 25°C                                            |                        | 95   | 115                    | μΑ    |

|                       |                                        | No Load, Output Low<br>T <sub>A</sub> = -40°C to +125°C                                 |                        |      | 120                    | μА    |

| $V_{POR}$             |                                        |                                                                                         |                        | 1.7  |                        | V     |

| INPUT BIA             | S CURRENT                              |                                                                                         |                        |      | ·                      |       |

| I <sub>B</sub>        | Input bias current (1)                 |                                                                                         |                        | 500  |                        | pA    |

| I <sub>B</sub>        | Input bias current (1) (3)             | T <sub>A</sub> = -40°C to +125°C                                                        | -5                     |      | 5                      | nA    |

| Ios                   | Input offset current                   |                                                                                         |                        | 10   |                        | pA    |

| INPUT CAI             | PACITANCE                              |                                                                                         |                        |      |                        |       |

| C <sub>ID</sub>       | Input Capacitance,<br>Differential     |                                                                                         |                        | 5    |                        | pF    |

| C <sub>IC</sub>       | Input Capacitance,<br>Common Mode      |                                                                                         |                        | 5    |                        | pF    |

| INPUT CO              | MMON MODE RANG                         | E                                                                                       |                        |      |                        |       |

| V <sub>CM-Range</sub> | Common-mode voltage range              | V <sub>CCI</sub> - V <sub>EEI</sub> = 2.7 V to 36 V<br>T <sub>A</sub> = -40°C to +125°C | V <sub>EEI</sub> - 0.2 |      | V <sub>CCI</sub> + 0.2 | V     |

| OUTPUT                | ·                                      |                                                                                         | -                      |      |                        |       |

| V <sub>OL</sub>       | Voltage swing from (V <sub>EEO</sub> ) | I <sub>SINK</sub> = 4 mA<br>T <sub>A</sub> = -40°C to +125°C                            |                        |      | 300                    | mV    |

| V <sub>OH</sub>       | Voltage swing from (V <sub>CCO</sub> ) | I <sub>SOURCE</sub> = 4 mA<br>T <sub>A</sub> = -40°C to +125°C                          |                        |      | 300                    | mV    |

| I <sub>OL</sub>       | Short-circuit current                  | Sinking<br>T <sub>A</sub> = -40°C to +125°C                                             |                        | 30   |                        | mA    |

| I <sub>OH</sub>       | Short-circuit current                  | Sourcing<br>T <sub>A</sub> = -40°C to +125°C                                            |                        | 30   |                        | mA    |

<sup>(1)</sup> Please see figure for  $I_{\text{BIAS}}$  vs  $V_{\text{ID}}$  performance curve

資料に関するフィードバック(ご意見やお問い合わせ)を送信

1

<sup>(2)</sup> Current shown is the sum of the current through VCCI and VCCO. Please see Supply Current graphs in Typical Characteristics section.

<sup>(3)</sup> This parameter is ensured by design and/or characterization and is not tested in production.

## **5.6 Switching Characteristics**

For  $V_{CCI}$  = 12 V,  $V_{EEI}$  = 0 V,  $V_{CCO}$  = 3.3 V,  $V_{EEO}$  = 0 V,  $V_{CM}$  = VS/2,  $C_L$  = 15 pF at  $T_A$  = 25°C (Unless otherwise noted)

| PARAMETER           |                                      | TEST CONDITIONS                                    | MIN | TYP MAX | UNIT |  |

|---------------------|--------------------------------------|----------------------------------------------------|-----|---------|------|--|

| Output              |                                      |                                                    |     | '       |      |  |

| T <sub>PD-HL</sub>  | Propagation delay time, high-to-low  | V <sub>OD</sub> = 10 mV, V <sub>UD</sub> = 100 mV  |     | 110     | ns   |  |

| T <sub>PD-HL</sub>  | Propagation delay time, high-to-low, | V <sub>OD</sub> = 100 mV, V <sub>UD</sub> = 100 mV |     | 65      | ns   |  |

| T <sub>PD-LH</sub>  | Propagation delay time, low-to-high  | V <sub>OD</sub> = 10 mV, V <sub>UD</sub> = 100 mV  |     | 110     | ns   |  |

| T <sub>PD-LH</sub>  | Propagation delay time, low-to-high  | V <sub>OD</sub> = 100 mV, V <sub>UD</sub> = 100 mV |     | 65      | ns   |  |

| T <sub>RISE</sub>   | Output Rise Time, 20% to 80%         | V <sub>OD</sub> = 100mV, V <sub>UD</sub> = 100mV   |     | 5       | ns   |  |

| T <sub>FALL</sub>   | Output Fall Time, 80% to 20%         | V <sub>OD</sub> = 100mV, V <sub>UD</sub> = 100mV   |     | 5       | ns   |  |

| F <sub>TOGGLE</sub> | Toggle Frequency                     | V <sub>ID</sub> = 200 mV                           |     | 7.5     | MHz  |  |

|                     | POWER ON TIME                        |                                                    |     |         |      |  |

| P <sub>ON</sub>     | Power on-time                        |                                                    |     | 80      | μs   |  |

Copyright © 2024 Texas Instruments Incorporated

8

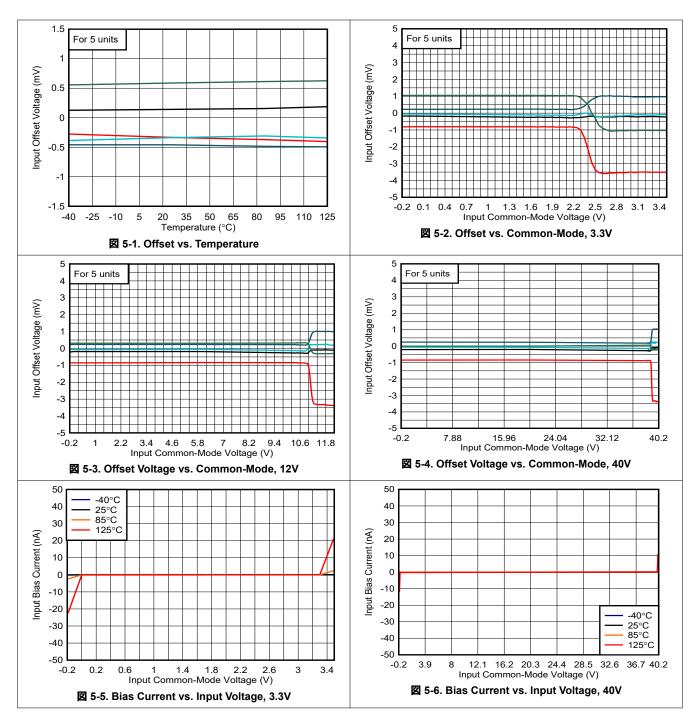

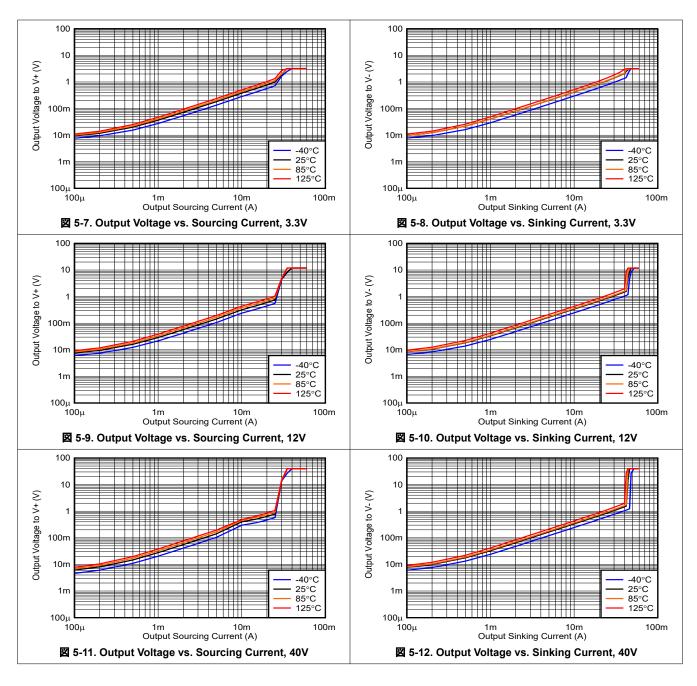

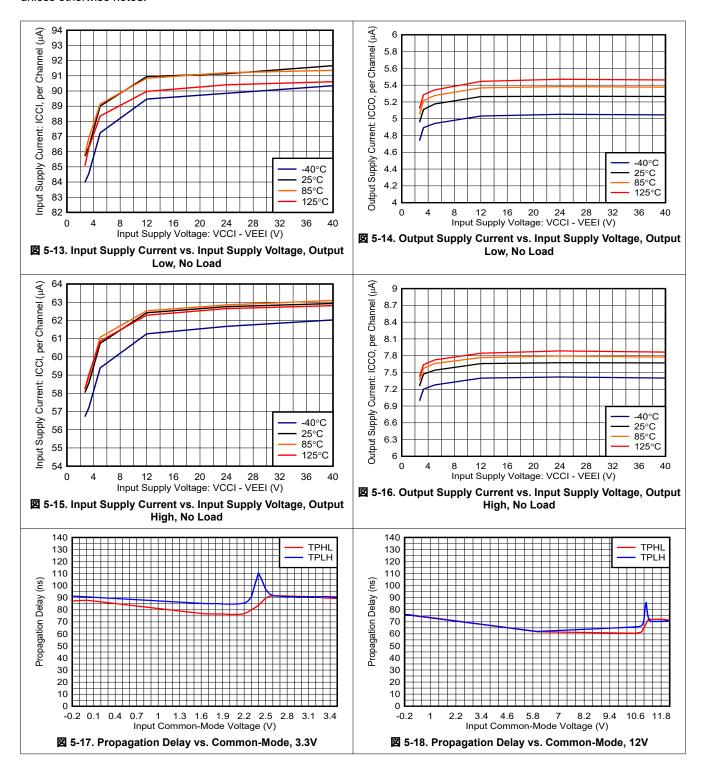

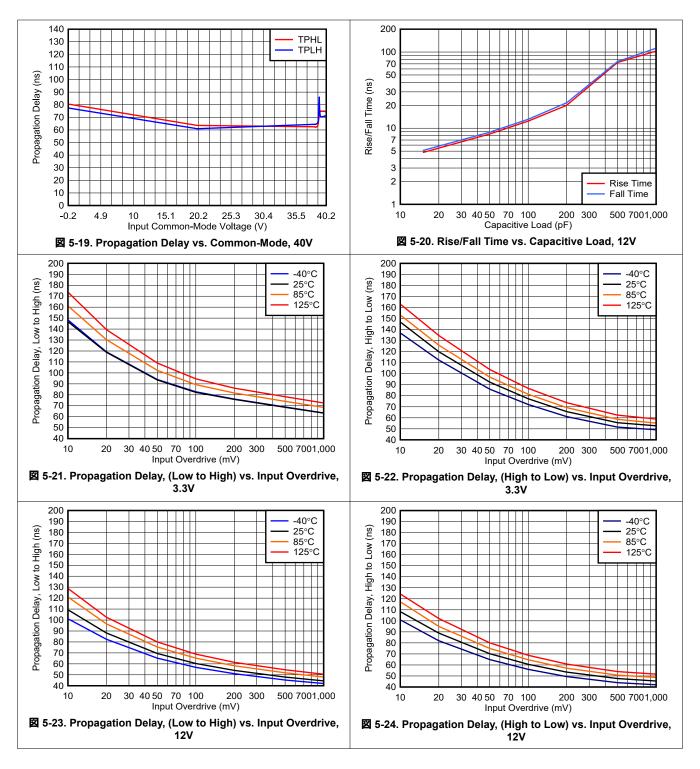

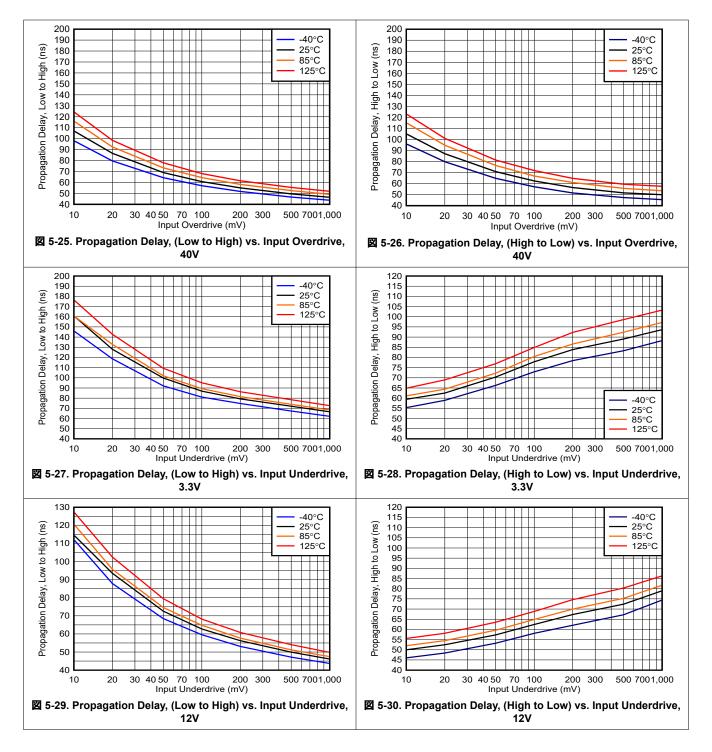

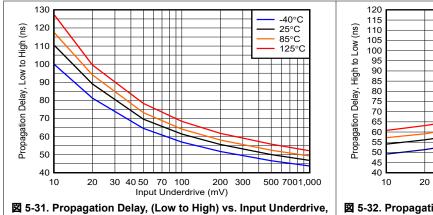

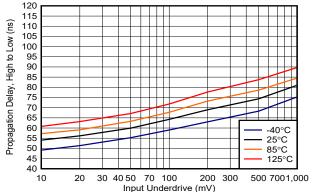

## **5.7 Typical Characteristics**

At  $T_A = 25$ °C,  $V_{CCI} - V_{EEI} = 12$ V,  $V_{CCO} - V_{EEO} = 3.3$ V,  $V_{CM} = VS/2$  V,  $C_L = 15$ pF, Input Overdrive = Input Underdrive = 100mV unless otherwise noted.

At  $T_A = 25$ °C,  $V_{CCI} - V_{EEI} = 12$ V,  $V_{CCO} - V_{EEO} = 3.3$ V,  $V_{CM} = VS/2$  V,  $C_L = 15$ pF, Input Overdrive = Input Underdrive = 100mV unless otherwise noted.

At  $T_A = 25$ °C,  $V_{CCI} - V_{EEI} = 12$ V,  $V_{CCO} - V_{EEO} = 3.3$ V,  $V_{CM} = VS/2$  V,  $C_L = 15$ pF, Input Overdrive = Input Underdrive = 100mV unless otherwise noted.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

11

At  $T_A = 25$ °C,  $V_{CCI} - V_{EEI} = 12$ V,  $V_{CCO} - V_{EEO} = 3.3$ V,  $V_{CM} = VS/2$  V,  $C_L = 15$ pF, Input Overdrive = Input Underdrive = 100mV unless otherwise noted.

At  $T_A = 25$ °C,  $V_{CCI} - V_{EEI} = 12$ V,  $V_{CCO} - V_{EEO} = 3.3$ V,  $V_{CM} = VS/2$  V,  $C_L = 15$ pF, Input Overdrive = Input Underdrive = 100mV unless otherwise noted.

13

$At T_A = 25^{\circ}C, V_{CCI} - V_{EEI} = 12V, V_{CCO} - V_{EEO} = 3.3V, V_{CM} = VS/2 \ V, C_L = 15 pF, Input Overdrive = Input Underdrive = 100 mV$ unless otherwise noted.

図 5-32. Propagation Delay, (High to Low) vs. Input Underdrive,

## **6 Detailed Description**

### 6.1 Overview

The TLV187x family are 40V high-speed comparators with push-pull output with separate input and output supplies allow for split supply capability on the inputs and level shifted outputs for downstream 5V or 3.3V logic devices. This makes the TLV187x well suited for bipolar zero-cross detection applications or Class-D audio amplifier systems. An internal power-on reset circuit makes sure that the output remains in a known state during power-up and power-down.

## 6.2 Functional Block Diagram

図 6-1. Block Diagram

#### **6.3 Feature Description**

The TLV187x (push-pull output) devices are high speed comparators with a typical propagation delay of 65ns and are capable of operating at voltages up to 40V. The separate input and output supplies make these comparators well-suited for applications that need bipolar signals to be level shifted to low voltage logic devices. This also eliminates the need for a pull-up resistor and offers propagation delay and edge-rate symmetry. These comparators also feature a rail-to-rail input stage capable of operating up to 200mV beyond the power supply rails combined with a maximum 3mV input offset and Power-On Reset (POR) for known start-up conditions.

15

### 6.4 Device Functional Modes

### 6.4.1 Separate Power Supplies

The TLV187x has a unique "floating" output stage where the input and output have separate power supplies to allow defining the output levels without external level shifting. This allows directly sensing bipolar input signals using a split supply, and ground-referenced, low-voltage logic output designed for directly driving processors, ASICs or gate drivers.

The VCCI and VEEI pins supply the power to the input stage and comparator core. The VCCO and VEEO pins provide the power for the output stage and set the output swing.

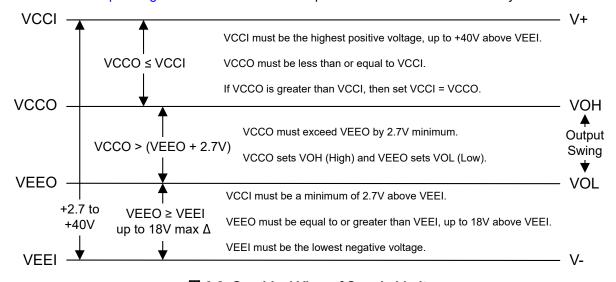

The VCCO and VEEO pins are bounded by the VEEI and VCCI pins. Please see the Absolute Maximum Ratings and Recommended Operating Conditions tables for the specifications. Below is a summary of the limits.

図 6-2. Graphical View of Supply Limits

VCCI is the positive supply for the input stage and sets the positive input voltage range (Positive VCM). VCCI must be a minimum of 2.7V and up to a maximum of 40V above VEEI to establish the total operating voltage  $(V_S)$ .

VCCO is the positive supply for the output stage, and sets the output high voltage level (VOH). VCCO must be at least 2.7V above VEEO and up to a maximum of VCCI.

VEEO is the negative supply for the output stage, and sets the output low voltage level (VOL). The VEEO pin must be equal to, or greater than the VEEI pin with up to a maximum +18V difference between the VEEI and VEEO pins.

VEEI is the negative supply for the input stage, and sets the negative input voltage range (negative VCM). The VEEI pin is the most negative "substrate" supply of the device. **Therefore the VEEI pin must be at the most negative circuit potential.** There must never be any more than 40V across the entire device with any combination of supply pins.

For example, an application where the input stage is VCCI = +15V, VEEI = -15V, and the output stage is using a single supply with VCCO = +3.3V and VEEO = GND is acceptable.

However, an application where VCCI = +5V, VEEI = GND, and the output stage using a split supply with VCCO = +12V and VEEO =-12V is **NOT** possible as that violates VEEO >= VEEI (VEEI is not the lowest negative potential) and VCCI < VCCO. If VCCI is instead connected to the +12V supply, and the VEEI is connected the -12V supply, that is acceptable.

Conversely, a negative input voltage application where VCCI = GND, VEEI = -12V, and the output stage using a single supply with VCCO = +3V and VEEO = GND is **NOT** possible as that violates VCCO >= VCCI (VEEO is

Copyright © 2024 Texas Instruments Incorporated

greater than VCCI). In this case, instead tie VCCI to the +3V output supply and that is acceptable (VCCI = VCCO).

Single supply applications are also possible, with both VEEO and VEEI at GND, as long as VCCO is less than or equal to VCCI (VCCO <= VCCI). So VCCO = +3V and VCCI = +12V is acceptable, but VCCO = +12V and VCCI = +3V is **NOT** possible (instead, tie VCCI to the +12V to make acceptable).

It is also possible to have the output swing between two positive voltage values, such as +2V and +5V, (i.e., VEEO= +2V, VCCO = +5V) as long as the above conditions are followed (VCCI >= +5V and VEEO > VEEI) and there is a minimum of +2.7V between VEEO and VCCO.

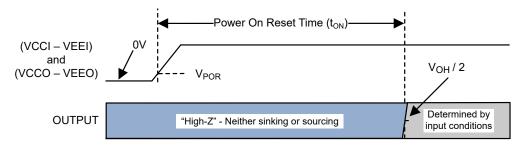

#### 6.4.2 Power-On Reset (POR)

The TLV187x devices have an internal Power-on-Reset (POR) circuit for known start-up or power-down conditions. While the power supplies are ramping up, the POR circuitry is activated for up to  $80\mu s$  after the  $V_{POR}$  threshold of 1.7V is crossed.

### The TLV187x Output is High Impedance ("Hi-Z") During the POR Period (t<sub>on</sub>).

The input and output POR thresholds are "AND'ed" together. When *BOTH* the input supply (VCCI-VEEI) *AND* the output supply (VCCO - VEEO) are greater than the  $V_{POR}$  voltage, then after a delay period ( $t_{ON}$ ), the comparator output reflects the state of the differential input ( $V_{ID}$ ).

図 6-3. Power-On Reset Timing Diagram

There is no delay on power down. The output enters the POR state immediately when both the supplies fall below  $V_{POR}$ .

### **6.4.3 Inputs**

#### 6.4.3.1 Rail-to-Rail Inputs

The input voltage range extends from 200mV below VEEI to 200mV above VCCI, maximizing input dynamic range. The input stage has ESD clamps to the VCCI supply line and therefore the input voltages must not exceed the supply voltages by more than 200mV. Do not apply signals to the rail to rail inputs with no supply voltage. To avoid damaging the inputs when exceeding the recommended input voltage range, an external resistor must be used to limit the current.

## 6.4.3.2 Unused Inputs

If a channel is not to be used, DO NOT tie the inputs together. Due to the high equivalent bandwidth and low offset voltage, tying the inputs directly together can cause high frequency oscillations as the device triggers on it's own internal wideband noise. Instead, the inputs should be tied to any available voltage that resides within the specified input voltage range and provides a minimum of 50mV differential voltage. For example, one input can be grounded and the other input connected to a reference voltage, or even VCCI.

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

17

## 6.4.4 Push-Pull Output

The TLV187x features a push-pull output stage capable of both sinking and sourcing current. This allows driving loads such as LED's and MOSFET gates, as well as eliminating the need for a power-wasting external pull-up resistor. The push-pull output must never be connected to another output.

Directly shorting the output to the supply rails can result in thermal runaway and eventual device destruction. If output shorts are possible, a series current limiting resistor in series with the output is recommended to limit the power dissipation.

Unused push-pull outputs must be left floating, and never tied to a supply, ground, or another output.

### 6.4.5 ESD Protection

The rail-to-rail input has ESD clamps to both VCCI and VEEI, as shown in the Functional Block Diagram, and therefore the input voltage must not exceed the VCCI and VEEO supply voltages by more than 200mV. Do not apply signals directly to the inputs with no supply voltage without series input current limiting.

If the inputs are to be connected to a low impedance source, such as a power supply or buffered reference line, or a signal that can be present while the power is off, TI recommends adding a current-limiting resistor in series with the input to limit any transient currents in case the clamps conduct. The current must be limited to 10mA or less. This series resistance can be part of any resistive input dividers or networks.

The TLV187x push-pull output has ESD clamps to both VCCO and VEEO, as shown in the Functional Block Diagram. The output must not exceed the output supply rails by more than 200mV. Output excursions can be caused by output trace ringing, inductive load kick-back, or externally induced transients.

Due to the high (<10ns) output edge rates, unless matched impedance traces are used, a small series resistor ( $\sim$ 33 to 100 $\Omega$ ) can be added in series with the output trace to dampen unmatched trace reflections. See the Layout Example in the Layout Guidelines section.

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

## 7 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 7.1 Application Information

### 7.1.1 Basic Comparator Definitions

### 7.1.1.1 Operation

The basic comparator compares the input voltage  $(V_{IN})$  on one input to a reference voltage  $(V_{REF})$  on the other input. In the  $\boxtimes$  7-1 example below, if  $V_{IN}$  is less than  $V_{REF}$ , the output voltage  $(V_O)$  is logic low  $(V_{OL})$ . If  $V_{IN}$  is greater than  $V_{REF}$ , the output voltage  $(V_O)$  is at logic high  $(V_{OH})$ . 表 7-1 summarizes the output conditions. The output logic can be inverted by simply swapping the input pins.

表 7-1. Output Conditions

| Inputs Condition | Output                                    |

|------------------|-------------------------------------------|

| IN+ > IN-        | HIGH (V <sub>OH</sub> )                   |

| IN+ = IN-        | Indeterminate (chatters - see Hysteresis) |

| IN+ < IN-        | LOW (V <sub>OL</sub> )                    |

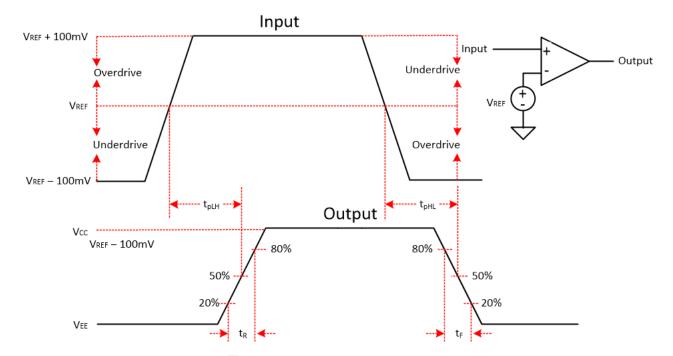

### 7.1.1.2 Propagation Delay

There is a delay between from when the input crosses the reference voltage and the output responds. This is called the Propagation Delay. Propagation delay can be different between high-to low and low-to-high input transitions. This is shown as  $t_{pLH}$  and  $t_{pHL}$  in  $\boxtimes$  7-1 and is measured from the mid-point of the input to the midpoint of the output.

☑ 7-1. Comparator Timing Diagram

### 7.1.1.3 Overdrive Voltage

The overdrive voltage,  $V_{OD}$ , is the amount of input voltage beyond the reference voltage (and not the total input peak-to-peak voltage). The overdrive voltage is 100mV as shown in the  $\boxtimes$  7-1 example. The overdrive voltage can influence the propagation delay ( $t_p$ ). The smaller the overdrive voltage, the longer the propagation delay, particularly when <100mV. If the fastest speeds are desired, TI recommends applying the highest amount of overdrive possible.

The risetime  $(t_r)$  and falltime  $(t_f)$  is the time from the 20% and 80% points of the output waveform.

### 7.1.2 Hysteresis

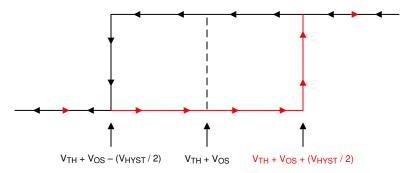

The basic comparator configuration can produce a noisy "chatter" output if the applied differential input voltage is near the comparator's offset voltage. This usually occurs when the input signal is moving very slowly across the switching threshold of the comparator. This problem can be prevented by adding external hysteresis to the comparator.

Since the TLV187x has a minimal amount of internal hysteresis of 2.7mV, external hysteresis can be applied in the form of a positive feedback loop that adjusts the trip point of the comparator depending on the current output state.

The hysteresis transfer curve is shown in  $\boxtimes$  7-2. This curve is a function of three components:  $V_{TH}$ ,  $V_{OS}$ , and  $V_{HVST}$ :

- V<sub>TH</sub> is the actual set voltage or threshold trip voltage.

- V<sub>OS</sub> is the internal offset voltage between V<sub>IN+</sub> and V<sub>IN-</sub>. This voltage is added to V<sub>TH</sub> to form the actual trip

point at which the comparator must respond to change output states.

- V<sub>HYST</sub> is the hysteresis (or trip window) that is designed to reduce comparator sensitivity to noise.

図 7-2. Hysteresis Transfer Curve

For more information, please see Application Note SBOA219 "Comparator with and without hysteresis circuit".

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

### 7.2 Typical Applications

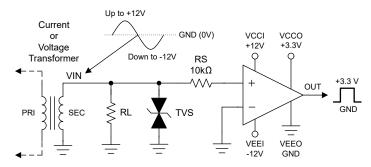

### 7.2.1 Accurate Bipolar Zero-Cross Detector

▼ 7-3 below shows a bipolar input zero cross detector circuit. The signal source is the secondary of a current or voltage transformer which outputs a bipolar (±100 mVp to ±12 Vp) AC signal that swings around 0V (GND). Since the input voltages are not AC coupled, level shifted or further attenuated, DC accurate millivolt zero cross accuracy is possible (even with distorted waveforms). This is due to the direct DC coupled input allowing belowground bipolar detection range afforded by the split ±12V supplies and rail-to-rail input of the TLV187x. DC coupling also avoids phase shifts caused by AC coupling and non-linearities caused by diode clamping. As the output does not require any further level-shifting or attenuation, the best possible output edge is available for the processor.

図 7-3. Bipolar Zero Cross Circuit using TLV187x

### 7.2.1.1 Design Requirements

表 7-2. Design Parameters

| PARAMETER            | VALUE                    |  |  |  |

|----------------------|--------------------------|--|--|--|

| Supply Voltage       | +3.3V, +12V and -12V     |  |  |  |

| Input Voltage Range  | Bipolar ±100mVp to ±12Vp |  |  |  |

| Threshold Level      | 0V (or GND)              |  |  |  |

| Frequency Range      | 50 - 1000Hz              |  |  |  |

| Logic Output Voltage | 0 to 3.3V                |  |  |  |

### 7.2.1.2 Detailed Design Procedure

$\gtrsim$  7-2 shows the requirements for the design. The input voltage is bipolar, ranging from  $\pm 100$ mV to  $\pm 12$ V, so split supplies on the comparator input are required.

RL is the required load resistance for the current or voltage transformer. The actual value is recommended by the transformer manufacturer.

RS limits the current into the ESD clamps when the comparator supplies are off and the AC signal can still be present from the transformer. All currents must be limited to 10mA or less (the less the better).

The TVS provides input protection against large transients that can pass through the transformer.

To accommodate the bipolar input range, the input supplies are set to VCCI = +12V, and VEEO = -12V. This allows for a full -12V to +12V input range.

The output supply is set to VCCO = +3.3V, and VEEO = GND for a 0 to 3.3V compatible logic output designed for direct input to a processor.

21

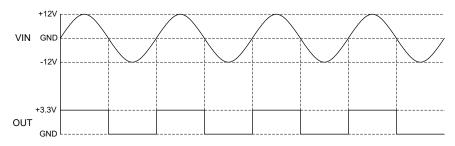

## 7.2.1.3 Application Performance Plots

☑ 7-4 shows the resulting output of the circuit. The output will be high when the AC waveform is above ground, and low when the waveform is below ground.

図 7-4. Typical Performance Plot for Zero-Cross Circuit

### 7.3 Power Supply Recommendations

Due to the fast output edges, it is critical to have bypass capacitors on the supply pin to prevent supply ringing and false triggers and oscillations. Bypass the supply directly at *each* device with a low ESR 0.1µF ceramic SMT bypass capacitor as directly as possible between the supply pins and ground. Narrow peak currents will be drawn during the output transition timedue to the push-pull output device. These narrow pulses can cause poorly bypassed supply lines and poor grounds to ring, possibly causing common mode variations that can eat into the input voltage range and create an inaccurate comparison or even oscillations or false-triggers

For more information, please see the Separate Power Supplies section for more information.

### 7.4 Layout

### 7.4.1 Layout Guidelines

Accurate comparator applications must maintain a stable power supply with minimized noise and glitches. Output rise and fall times are in the tens of nanoseconds, and must be treated as high speed logic devices.

The bypass capacitors must be as close to the supply pin as possible and connected to a solid ground plane, and preferably directly between the VCCx or VEEx and GND pins. Pads need have two or more vias to minimize inductance to the power plane. Shared ground islands need multiple vias to the main ground plane.

Minimize coupling between outputs and inputs to prevent output oscillations. Do not run output and input traces in parallel unless there is a GND trace between output to reduce coupling. When series resistance is added to inputs (RIN), place resistor close to the device.

A low value (<100 ohms) resistor (ROUT) can be added in series with the output to dampen any ringing or reflections on long, non-impedance controlled traces. For best edge shapes, controlled impedance traces with back-terminations must be used when routing long distances.

#### 7.4.2 Layout Example

図 7-5. Layout Example

Copyright © 2024 Texas Instruments Incorporated

## 8 Device and Documentation Support

### 8.1 Documentation Support

#### 8.1.1 Related Documentation

Analog Engineers Circuit Cookbook: Amplifiers (See Comparators section) - SLYY137

Precision Design, Comparator with Hysteresis Reference Design— TIDU020

Window comparator circuit - SBOA221

Reference Design, Window Comparator Reference Design— TIPD178

Comparator with and without hysteresis circuit - SBOA219

Inverting comparator with hysteresis circuit - SNOA997

Non-Inverting Comparator With Hysteresis Circuit - SBOA313

A Quad of Independently Func Comparators - SNOA654

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

#### 8.4 Trademarks

テキサス・インスツルメンツ E2E<sup>™</sup> is a trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

## 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

#### 9 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE       | REVISION | NOTES           |  |  |  |  |

|------------|----------|-----------------|--|--|--|--|

| March 2024 | *        | Initial Release |  |  |  |  |

Product Folder Links: TLV1872

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

23

JAJSRI6 - MARCH 2024

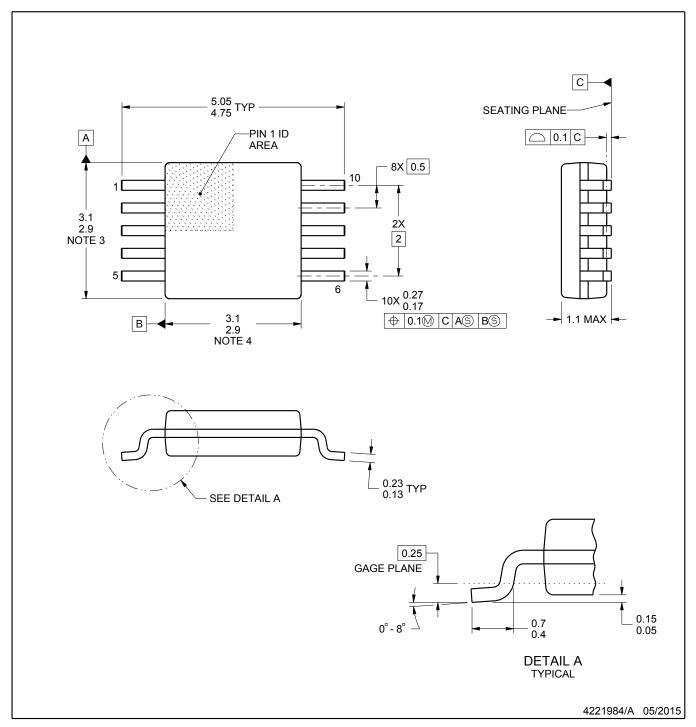

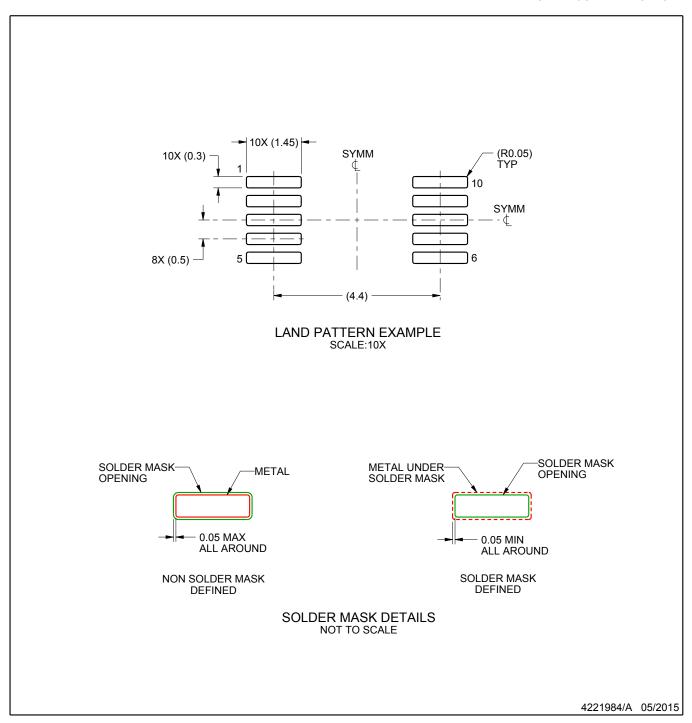

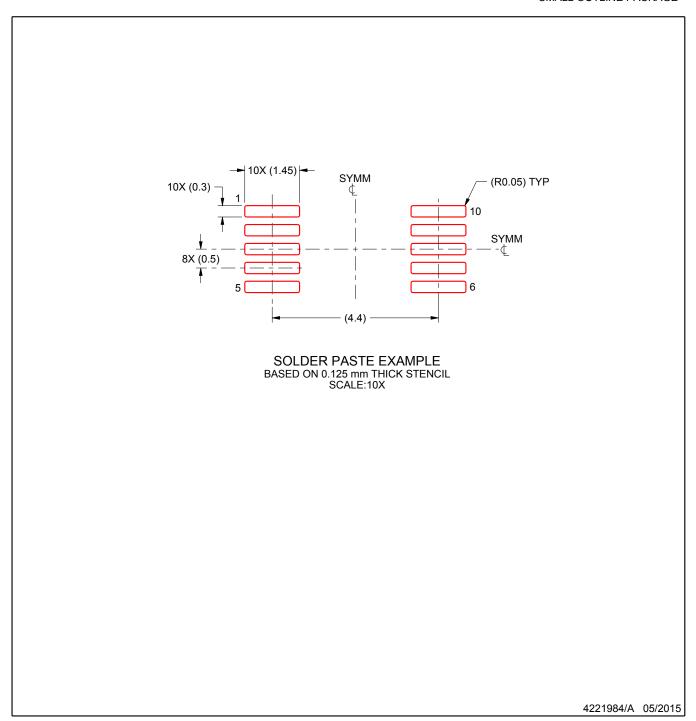

## 10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Product Folder Links: TLV1872

Copyright © 2024 Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated www.ti.com 28-Mar-2024

#### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

| TLV1872DGSR      | ACTIVE        | VSSOP        | DGS                | 10   | 2500           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | TL72                 | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

SMALL OUTLINE PACKAGE

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187, variation BA.

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated