SBOS340C-DECEMBER 2006-REVISED AUGUST 2008

# Single 2:1 High-Speed Video Multiplexer

### **FEATURES**

- 700MHz SMALL-SIGNAL BANDWIDTH (A<sub>V</sub> = +2)

- 425MHz, 4V<sub>PP</sub> BANDWIDTH

- 0.1dB GAIN FLATNESS to 200MHz

- 4ns CHANNEL SWITCHING TIME

- LOW SWITCHING GLITCH: 40mV<sub>PP</sub>

- 3100V/µs SLEW RATE

- 0.025%/0.025° DIFFERENTIAL GAIN, PHASE

- HIGH GAIN ACCURACY: 2.0V/V ±0.4%

## **APPLICATIONS**

- RGB SWITCHING

- LCD PROJECTOR INPUT SELECT

- WORKSTATION GRAPHICS

- ADC INPUT MUX

- DROP-IN UPGRADE TO LT1675-1

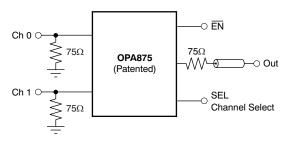

2:1 Video Multiplexer

## DESCRIPTION

The OPA875 offers a very wideband, single-channel 2:1 multiplexer in an SO-8 or a small MSOP-8 package. Using only 11mA, the OPA875 provides a gain of +2 video amplifier channel with greater than 425MHz large-signal bandwidth  $(4V_{PP})$ . Gain accuracy and switching glitch are improved over earlier solutions using a new input stage switching approach. This technique uses current steering as the input switch while maintaining an overall closed-loop design. With greater than 700MHz small-signal bandwidth at a gain of 2, the OPA875 gives a typical 0.1dB gain flatness to greater than 200MHz.

System power may be reduced using the chip enable feature for the OPA875. Taking the chip enable line high powers down the OPA875 to less than  $300\mu$ A total supply current. Muxing multiple OPA875 outputs together, then using the chip enable to select which channels are active, increases the number of possible inputs.

Where three channels are required, consider using the OPA3875 for the same level of performance.

### **OPA875 RELATED PRODUCTS**

|         | DESCRIPTION           |

|---------|-----------------------|

| OPA3875 | Triple-Channel OPA875 |

| OPA692  | 225MHz Video Buffer   |

| OPA693  | 700MHz Video Buffer   |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

### SBOS340C-DECEMBER 2006-REVISED AUGUST 2008

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|------------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| OPA875  | SO-8             | D                     | -40°C to +85°C                    | OPA875             | OPA875ID           | Rails, 75                    |

| UFA075  | 30-6             | D                     | -40 C 10 +65 C                    | UFA675             | OPA875IDR          | Tape and Reel, 2500          |

| 004075  |                  | DOK                   | -40°C to +85°C                    |                    |                    | Tape and Reel, 250           |

| OPA875  | MSOP-8           | MSOP-8 DGK            |                                   | BPL                | OPA875IDGKR        | Tape and Reel, 2500          |

### **ORDERING INFORMATION**

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating temperature range, unless otherwise noted.

|                                           | OPA875          | UNIT        |

|-------------------------------------------|-----------------|-------------|

| Power Supply                              | ±6.5            | V           |

| Internal Power Dissipation                | See Therm       | al Analysis |

| Input Voltage Range                       | ±V <sub>S</sub> | V           |

| Storage Temperature Range                 | -65 to +125     | C°          |

| Lead Temperature (soldering, 10s)         | +260            | °C          |

| Operating Junction Temperature            | +150            | °C          |

| Continuous Operating Junction Temperature | +140            | °C          |

| ESD Rating:                               |                 |             |

| Human Body Model (HBM)                    | 2000            | V           |

| Charged Device Model (CDM)                | 1500            | V           |

| Machine Model (MM)                        | 200             | V           |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

### Table 1. TRUTH TABLE

|        | OPA875 |                  |  |  |  |  |  |  |  |

|--------|--------|------------------|--|--|--|--|--|--|--|

| SELECT | ENABLE | V <sub>OUT</sub> |  |  |  |  |  |  |  |

| 1      | 0      | R0               |  |  |  |  |  |  |  |

| 0      | 0      | R1               |  |  |  |  |  |  |  |

| Х      | 1      | Off              |  |  |  |  |  |  |  |

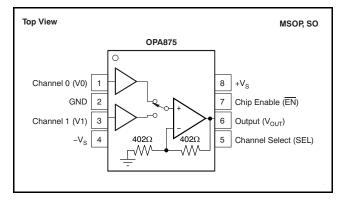

### **PIN CONFIGURATION**

SBOS340C-DECEMBER 2006-REVISED AUGUST 2008

### www.ti.com

## ELECTRICAL CHARACTERISTICS: $V_s = \pm 5V$

At G = +2 and  $R_L$  = 150 $\Omega$ , unless otherwise noted.

|                                              |                                                                                 |            | OPA                  | <b>\875</b>                    |                                  |                  |             |                              |

|----------------------------------------------|---------------------------------------------------------------------------------|------------|----------------------|--------------------------------|----------------------------------|------------------|-------------|------------------------------|

|                                              |                                                                                 | ТҮР        |                      | IIN/MAX OVE                    |                                  |                  |             |                              |

| PARAMETER                                    | CONDITIONS                                                                      | +25°C      | +25°C <sup>(2)</sup> | 0°C to<br>+70°C <sup>(3)</sup> | -40°C to<br>+85°C <sup>(3)</sup> | UNITS            | MIN/<br>MAX | TEST<br>LEVEL <sup>(1)</sup> |

|                                              | See Figure 1                                                                    |            |                      |                                |                                  | 00               |             |                              |

| Small-Signal Bandwidth                       | $V_{\Omega} = 200 \text{mV}_{\text{PP}}, \text{R}_{\text{I}} = 150 \Omega$      | 700        | 525                  | 515                            | 505                              | MHz              | min         | В                            |

| Large-Signal Bandwidth                       | $V_{O} = 4V_{PP}, R_{L} = 150\Omega$                                            | 425        | 390                  | 380                            | 370                              | MHz              | min         | В                            |

| Bandwidth for 0.1dB Gain Flatness            | $V_{O} = 200 \text{mV}_{PP}$                                                    | 200        |                      |                                |                                  | MHz              | typ         | с                            |

| Maximum Small-Signal Gain                    | $V_0 = 200 \text{mV}_{PP}, \text{ R}_L = 150\Omega, \text{ f} = 5 \text{MHz}$   | 2.0        | 2.02                 | 2.03                           | 2.05                             | V/V              | max         | В                            |

| Minimum Small-Signal Gain                    | $V_{0} = 200 \text{mV}_{PP}, \text{R}_{1} = 150\Omega, \text{f} = 5 \text{MHz}$ | 2.0        | 1.98                 | 1.97                           | 1.95                             | V/V              | min         | В                            |

| SFDR                                         | $10MHz, V_0 = 2V_{PP}, R_L = 150\Omega$                                         | -66        | -64                  | -63                            | -62                              | dBc              | max         | В                            |

| Input Voltage Noise                          | f > 100kHz                                                                      | 6.7        | 7.0                  | 7.2                            | 7.4                              | nV/√Hz           | max         | В                            |

| Input Current Noise                          | f > 100kHz                                                                      | 3.8        | 4.2                  | 4.6                            | 4.9                              | pA/√Hz           | max         | В                            |

| NTSC Differential Gain                       | $R_1 = 150\Omega$                                                               | 0.025      | 7.2                  | 4.0                            | 4.0                              | %                | typ         | c                            |

| NTSC Differential Phase                      | $R_{\rm I} = 150\Omega$                                                         | 0.025      |                      |                                |                                  |                  | typ         | c                            |

| Slew Rate                                    | $V_{\rm O} = \pm 2V$                                                            | 3100       | 2800                 | 2700                           | 2600                             | V/µs             | min         | В                            |

| Rise Time and Fall Time                      | $V_0 = \pm 2 V$<br>$V_0 = 0.5V$ Step                                            |            | 2000                 | 2700                           | 2000                             |                  |             | С                            |

| Rise Time and Fall Time                      | а I.                                                                            | 460<br>600 |                      |                                |                                  | ps               | typ         | c                            |

|                                              | V <sub>O</sub> = 1.4V Step                                                      | 600        |                      |                                |                                  | ps               | typ         | L L                          |

| CHANNEL-TO-CHANNEL PERFORMANCE<br>Gain Match | D 4500                                                                          | 0.05       | ±0.25                | ±0.3                           | ±0.35                            | %                |             | А                            |

|                                              | $R_{L} = 150\Omega$                                                             | ±0.05      |                      |                                |                                  |                  | max         |                              |

| Output Offset Voltage Mismatch               | ( 500 ML D (500                                                                 | ±3         | ±9                   | ±10                            | ±12                              | mV               | max         | A                            |

| Crosstalk                                    | $f < 50MHz, R_L = 150\Omega$                                                    | -65        |                      |                                |                                  | dB               | typ         | С                            |

| CHANNEL AND CHIP-SELECT<br>PERFORMANCE       |                                                                                 |            |                      |                                |                                  |                  |             |                              |

| SEL (Channel Select) Switching Time          | $R_L = 150\Omega$                                                               | 4          |                      |                                |                                  | ns               | typ         | С                            |

| EN (Chip Select) Switching Time              | Turn On                                                                         | 9          |                      |                                |                                  | ns               | typ         | С                            |

|                                              | Turn Off                                                                        | 60         |                      |                                |                                  | ns               | typ         | С                            |

| SEL (Channel Select) Switching Glitch        | Both Inputs to Ground, At Matched Load                                          | 40         |                      |                                |                                  | $mV_{PP}$        | typ         | С                            |

| EN (Chip-Select) Switching Glitch            | Both Inputs to Ground, At Matched Load                                          | 30         |                      |                                |                                  | mV <sub>PP</sub> | typ         | С                            |

| Off Isolation                                | 50MHz, Chip Disabled ( $\overline{EN}$ = High)                                  | -70        |                      |                                |                                  | dB               | typ         | С                            |

| Maximum Logic 0                              | EN, A0, A1                                                                      |            | 0.8                  | 0.8                            | 0.8                              | V                | max         | А                            |

| Minimum Logic 1                              | EN, A0, A1                                                                      |            | 2.0                  | 2.0                            | 2.0                              | V                | min         | А                            |

| EN Logic Input Current                       | 0V to 4.5V                                                                      | 25         | 35                   | 45                             | 50                               | μA               | max         | А                            |

| SEL Logic Input Current                      | 0V to 4.5V                                                                      | 55         | 70                   | 85                             | 100                              | μA               | max         | А                            |

| DC PERFORMANCE                               |                                                                                 |            |                      |                                |                                  |                  |             |                              |

| Output Offset Voltage                        | $R_{IN} = 0\Omega, G = +2V/V$                                                   | ±2.5       | ±14                  | ±15.8                          | ±17                              | mV               | max         | A                            |

| Average Output Offset Voltage Drift          |                                                                                 |            |                      | ±50                            | ±50                              | μV/°C            | max         | В                            |

| Input Bias Current                           |                                                                                 | ±5         | ±18                  | ±19.5                          | ±20.5                            | μΑ               | max         | А                            |

| Average Input Bias Current Drift             |                                                                                 |            | -                    | ±40                            | ±40                              | nA/°C            | max         | В                            |

| Gain Error (from 2V/V)                       | $V_0 = \pm 2V$                                                                  | 0.4        | 1.4                  | 1.5                            | 1.6                              | %                | max         | A                            |

| INPUT                                        |                                                                                 |            |                      |                                |                                  | ,,,              |             |                              |

| Input Voltage Range                          |                                                                                 | ±2.8       |                      |                                |                                  | V                | min         | с                            |

| Input Resistance                             |                                                                                 | 1.75       |                      |                                |                                  | MΩ               | typ         | c                            |

| Input Capacitance                            | Channel Selected                                                                | 0.9        |                      |                                |                                  | pF               | typ         | c                            |

|                                              | Channel Deselected                                                              | 0.9        |                      |                                |                                  | pF<br>pF         |             | c                            |

|                                              |                                                                                 |            |                      |                                |                                  |                  | typ         | c                            |

|                                              | Chip Disabled                                                                   | 0.9        |                      |                                |                                  | pF               | typ         | C                            |

(1) Test levels: (A) 100% tested at +25°C. Over temperature limits set by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

(2) Junction temperature = ambient for +25°C tested specifications.

(3) Junction temperature = ambient at low temperature limit; junction temperature = ambient +14°C at high temperature limit for over temperature specifications.

# ELECTRICAL CHARACTERISTICS: $V_s = \pm 5V$ (continued)

At G = +2 and  $R_{L}$  = 150 $\Omega,$  unless otherwise noted.

|                                         |         |                                |            | OPA                  | <b>\875</b>                    |                                  |       |             |                              |

|-----------------------------------------|---------|--------------------------------|------------|----------------------|--------------------------------|----------------------------------|-------|-------------|------------------------------|

|                                         |         |                                | ТҮР        |                      | IIN/MAX OVE                    |                                  |       |             |                              |

| PARAMETER                               |         | CONDITIONS                     | +25°C      | +25°C <sup>(2)</sup> | 0°C to<br>+70°C <sup>(3)</sup> | -40°C to<br>+85°C <sup>(3)</sup> | UNITS | MIN/<br>MAX | TEST<br>LEVEL <sup>(1)</sup> |

| OUTPUT                                  |         |                                |            |                      |                                |                                  |       |             |                              |

| Output Voltage Range                    |         |                                | ±3.5       | ±3.4                 | ±3.35                          | ±3.3                             | V     | min         | А                            |

| Output Current                          |         | $V_{O}$ = 0V, Linear Operation | ±70        | ±50                  | ±45                            | ±40                              | mA    | min         | А                            |

| Output Resistance                       |         | Chip enabled                   | 0.3        |                      |                                |                                  | Ω     | typ         | С                            |

|                                         |         | Chip Disabled, Maximum         | 800        | 912                  | 915                            | 918                              | Ω     | max         | А                            |

|                                         |         | Chip Disabled, Minimum         | 800        | 688                  | 685                            | 682                              | Ω     | min         | А                            |

| Output Capacitance                      |         | Chip Disabled                  | 2          |                      |                                |                                  | pF    | typ         | С                            |

| POWER SUPPLY                            |         |                                |            |                      |                                |                                  |       |             |                              |

| Specified Operating Voltage             |         |                                | ±5         |                      |                                |                                  | V     | typ         | С                            |

| Minimum Operating Voltage               |         |                                |            | ±3.0                 | ±3.0                           | ±3.0                             | V     | min         | В                            |

| Maximum Operating Voltage               |         |                                |            | ±6.0                 | ±6.0                           | ±6.0                             | V     | max         | А                            |

| Maximum Quiescent Current               |         | Chip Selected, $V_S = \pm 5V$  | 11         | 11.5                 | 11.7                           | 12                               | mA    | max         | А                            |

| Minimum Quiescent Current               |         | Chip Selected, $V_S = \pm 5V$  | 11         | 10                   | 9.5                            | 9                                | mA    | min         | А                            |

| Maximum Quiescent Current               |         | Chip Deselected                | 300        | 500                  | 550                            | 600                              | μA    | max         | А                            |

| Power-Supply Rejection Ratio            | (+PSRR) | Input-Referred                 | 56         | 50                   | 48                             | 47                               | dB    | min         | А                            |

|                                         | (-PSRR) | Input-Referred                 | 55         | 51                   | 49                             | 48                               | dB    | min         | А                            |

| THERMAL CHARACTERISTICS                 |         |                                |            |                      |                                |                                  |       |             |                              |

| Specified Operating Range D Pacl        | kage    |                                | -40 to +85 |                      |                                |                                  | °C    | typ         | С                            |

| Thermal Resistance $\theta_{\text{JA}}$ |         | Junction-to-Ambient            |            |                      |                                |                                  |       |             |                              |

| D                                       | SO-8    |                                | +100       |                      |                                |                                  | °C/W  | typ         | С                            |

| DGK                                     | MSOP-8  |                                | +140       |                      |                                |                                  | °C/W  | typ         | С                            |

4

Copyright © 2006–2008, Texas Instruments Incorporated

SBOS340C-DECEMBER 2006-REVISED AUGUST 2008

### www.ti.com

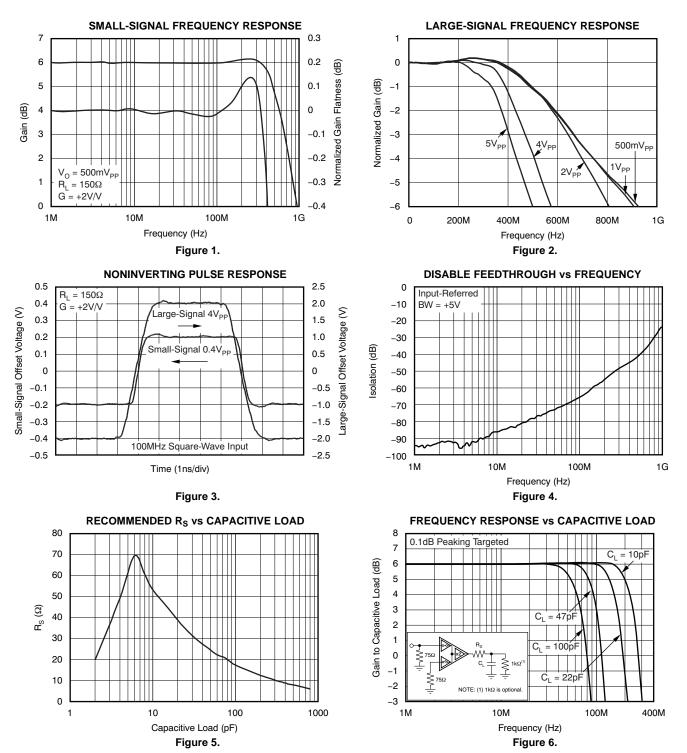

## TYPICAL CHARACTERISTICS: $V_s = \pm 5V$

At G = +2 and  $R_L$  = 150 $\Omega$ , unless otherwise noted.

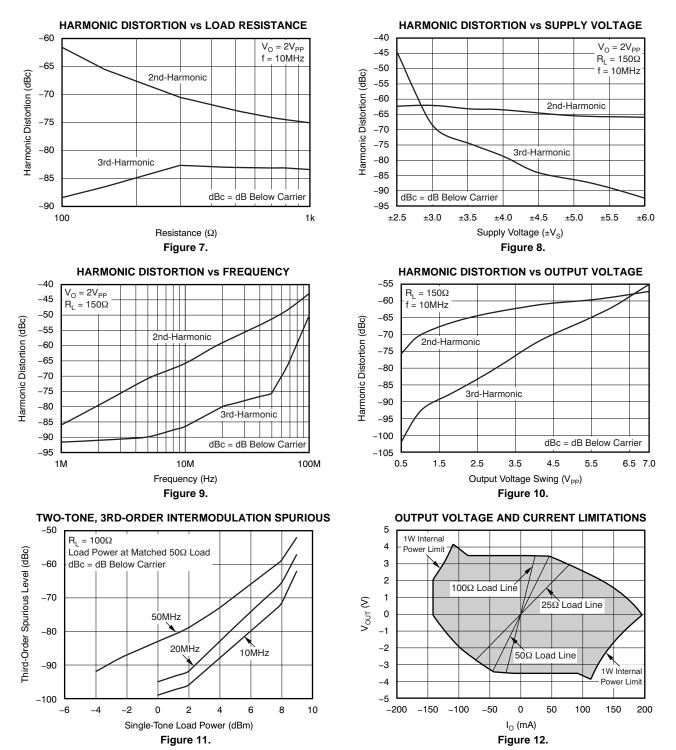

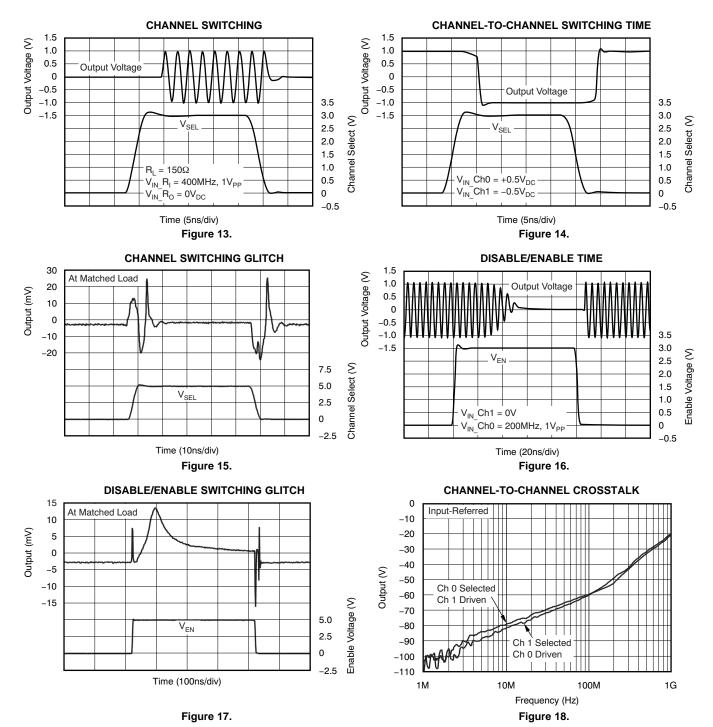

## TYPICAL CHARACTERISTICS: V<sub>s</sub> = ±5V (continued)

### At G = +2 and $R_L$ = 150 $\Omega$ , unless otherwise noted.

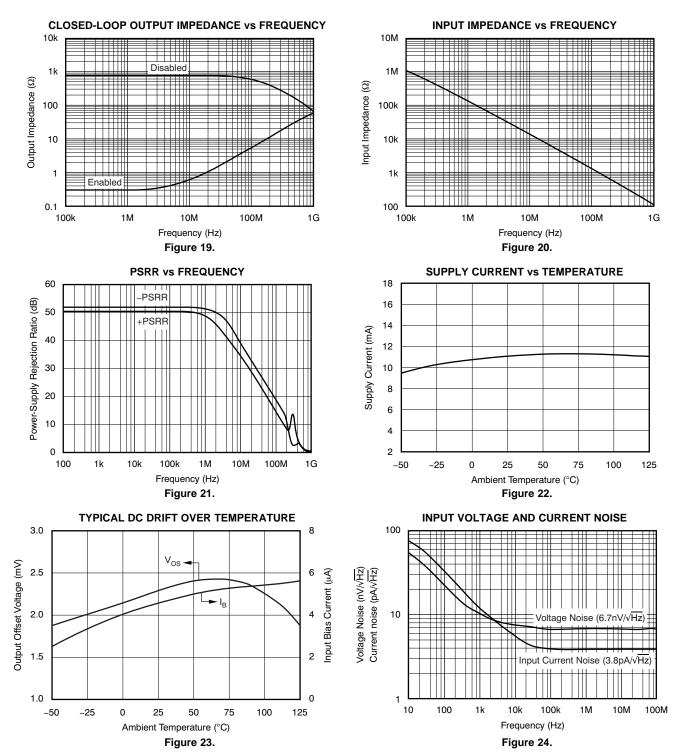

## TYPICAL CHARACTERISTICS: V<sub>s</sub> = ±5V (continued)

### At G = +2 and $R_L$ = 150 $\Omega$ , unless otherwise noted.

## TYPICAL CHARACTERISTICS: $V_s = \pm 5V$ (continued)

At G = +2 and  $R_L$  = 150 $\Omega$ , unless otherwise noted.

## **APPLICATIONS INFORMATION**

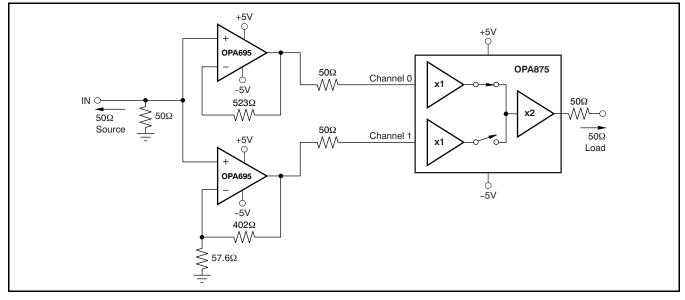

### **1-BIT HIGH-SPEED PGA**

The OPA875 can be used as a 1-bit, high-speed programmable gain amplifier (PGA) when used in conjunction with another amplifier. Figure 25 shows the OPA695 used twice with one amplifier configured in a unity-gain structure, and the other amplifier configured in a gain of +8V/V.

When channel 0 is selected, the overall gain to the matched load of the OPA875 is 0dB. When channel 1 is selected, this circuit delivers an 18dB gain to the matched load.

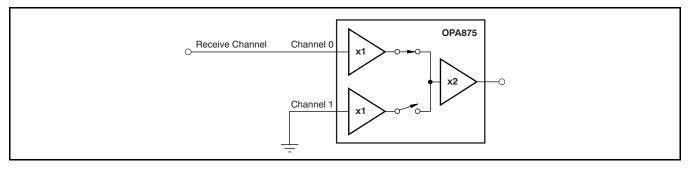

### TRANSMIT/RECEIVE SWITCH

The OPA875 can be used as a transmit/receive switch in which the receive channel is disconnected, when the OPA875 is switched from channel 0 to channel 1, to prevent the transmit pulse from going through the receive signal chain. This architecture is shown in Figure 26.

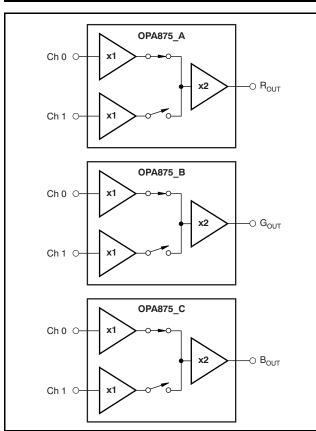

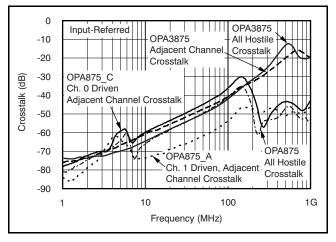

### HIGH ISOLATION RGB VIDEO MUX

Three OPA875s can be used as a triple, 2:1 video MUX (see Figure 27). This configuration has the advantage of having higher R to G to B isolation than a comparable and more integrated solution does, such as the OPA3875, especially at higher frequencies. This comparison is shown in Figure 28.

Figure 25. 1-Bit, High-Speed PGA

Figure 26. Transmit/Receive Switch

SBOS340C-DECEMBER 2006-REVISED AUGUST 2008

Figure 27. High Isolation RGB Video MUX

Figure 28. All Hostile and Adjacent Channel Crosstalk

The configuration of the three OPA875 devices used is shown in Figure 27. Note that for the test, the OPA875\_B was measured when both the OPA875\_A and OPA875\_C were driven for all hostile crosstalk and only the OPA875\_A or OPA875\_C was driven for the adjacent channel crosstalk.

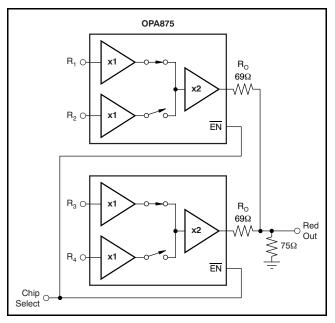

## **4-INPUT RGB ROUTER**

Two OPA875s can be used together to form a four-input RGB router. The router for the red component is shown in Figure 29.

Figure 29. 4-Input RGB Router

When connecting OPA875 outputs together, maintain a gain of +1 at the load. The OPA875 operates at a gain of +6dB; thus, matching resistance must be selected to achieve –6dB attenuation.

The set of equations to solve are shown in Equation 1 and Equation 2. Here, the impedance of interest is  $Z_0 = 75\Omega$ .

$$R_{O} = Z_{O} \parallel (R + R_{F} + R_{G})$$

$$1 + \frac{R_{F}}{R_{G}} = 2$$

$$R_{F} + R_{G} = 804\Omega$$

(1)

$$R_{\rm F} = R_{\rm G} \tag{2}$$

Solving for  $R_0$  with *n* devices connected together, we get Equation 3:

$$R_{0} = \frac{75 \times (n-1) + 804}{2} \times \left[ \sqrt{1 + \frac{241200}{\left[75 \times (n-1) + 804\right]^{2}}} - 1 \right]$$

(3)

Results for *n* varying from 2 to 6 are given in Table 2.

### Table 2. Series Resistance versus Number of Parallel Outputs

| NUMBER OF OPA875s | R <sub>0</sub> (Ω) |

|-------------------|--------------------|

| 2                 | 69                 |

| 3                 | 63.94              |

| 4                 | 59.49              |

| 5                 | 55.59              |

| 6                 | 52.15              |

The two major limitations of this circuit are the device requirements for each OPA875 and the acceptable return loss because of the mismatch between the load  $(75\Omega)$  and the matching resistor.

### **DESIGN-IN TOOLS**

### **DEMONSTRATION FIXTURES**

Two printed circuit boards (PCBs) are available to assist in the initial evaluation of circuit performance using the OPA875. These fixtures are offered free of charge as unpopulated PCBs, delivered with a user's guide. The summary information for these fixtures is shown in Table 3.

**Table 3. OPA875 Demonstration Fixtures**

| PRODUCT    | PACKAGE | ORDERING NUMBER | LITERATURE<br>NUMBER |

|------------|---------|-----------------|----------------------|

| OPA875IDGK | MSOP-8  | DEM-OPA-MSOP-1B | SBOU044              |

| OPA875ID   | SO-8    | DEM-OPA-SO-1D   | SBOU049              |

The demonstration fixture can be requested at the Texas Instruments web site at (www.ti.com) through the OPA875 product folder.

# MACROMODELS AND APPLICATIONS SUPPORT

Computer simulation of circuit performance using SPICE is often useful when analyzing the performance of analog circuits and systems. This is particularly true for video and RF amplifier circuits where parasitic capacitance and inductance can have a major effect on circuit performance. A SPICE model for the OPA875 is available through the Texas Instruments web site at www.ti.com. These models do a good job of predicting small-signal AC and transient performance under a wide variety of operating conditions. They do not do as well in predicting the harmonic distortion or dG/dP characteristics. These models do not attempt to distinguish between the package types in their small-signal AC performance.

## **OPERATING SUGGESTIONS**

### DRIVING CAPACITIVE LOADS

One of the most demanding, yet very common load conditions is capacitive loading. Often, the capacitive load is the input of an ADC-including additional external capacitance that may be recommended to improve ADC linearity. A high-speed device such as the OPA875 can be very susceptible to decreased stability and closed-loop response peaking when a capacitive load is placed directly on the output pin. When the device open-loop output resistance is considered, this capacitive load introduces an additional pole in the signal path that can decrease the phase margin. Several external solutions to this problem have been suggested. When the primary considerations are frequency response flatness, pulse response fidelity, and/or distortion, the simplest and most effective solution is to isolate the capacitive load from the feedback loop by inserting a series isolation resistor between the amplifier output and the capacitive load. This isolation resistor does not eliminate the pole from the loop response, but rather shifts it and adds a zero at a higher frequency. The additional zero acts to cancel the phase lag from the capacitive load pole, thus increasing the phase margin and improving stability.

The Typical Characteristics show the recommended  $R_S$  versus capacitive load and the resulting frequency response at the load; see Figure 5. Parasitic capacitive loads greater than 2pF can begin to degrade the performance of the OPA875. Long PCB traces, unmatched cables, and connections to multiple devices can easily cause this value to be exceeded. Always consider this effect carefully, and add the recommended series resistor as close as possible to the OPA875 output pin (see the Board Layout Guidelines section).

### DC ACCURACY

The OPA875 offers excellent DC signal accuracy. Parameters that influence the output DC offset voltage are:

- Output offset voltage

- Input bias current

- Gain error

- Power-supply rejection ratio

- Temperature

Leaving both temperature and gain error parameters aside, the output offset voltage envelope can be described as shown in Equation 4:

$$V_{OSO\_envelope} = V_{OSO} + (R_{S} \cdot I_{b}) \times G \pm |5 - (V_{S+})| \times 10^{-\frac{PSRR+}{20}} \pm |-5 - (V_{S-})| \times 10^{-\frac{PSRR-}{20}}$$

(4)

With:

V<sub>oso</sub>: Output offset voltage

R<sub>s</sub>: Input resistance seen by R0, R1, G0, G1, B0, or B1.

I<sub>b</sub>: Input bias current

**G:** Gain

V<sub>S+</sub>: Positive supply voltage V<sub>S-</sub>: Negative supply voltage **PSRR+**: Positive supply PSRR

PSRR-: Negative supply PSRR

Evaluating the front-page schematic, using a worst-case,  $+25^{\circ}$ C offset voltage, bias current and PSRR specifications and operating at  $\pm 6V$ , gives a worst-case output equal to Equation 5:

±14mV + 75Ω x ±18μA x 2 ±

$$|5 - 6| \times 10^{-\frac{50}{20}}$$

±  $|-5 - (-6)| \times 10^{-\frac{51}{20}}$

= ±22.7mV

### **DISTORTION PERFORMANCE**

The OPA875 provides good distortion performance into a  $100\Omega$  load on ±5V supplies. Relative to alternative solutions, it provides exceptional performance into lighter loads. Generally, until the fundamental signal reaches very high frequency or power levels, the 2nd-harmonic dominates the distortion with a negligible 3rd-harmonic component. Focusing then on the 2nd-harmonic, increasing the load impedance improves distortion directly. Also, providing an additional supply decoupling capacitor ( $0.01\mu$ F) between the supply pins (for bipolar operation) improves the 2nd-order distortion slightly (3dB to 6dB).

In most op amps, increasing the output voltage swing increases harmonic distortion directly. The Typical Characteristics show the 2nd-harmonic increasing at a little less than the expected 2X rate while the 3rd-harmonic increases at a little less than the expected 3X rate. Where the test power doubles, the 2nd-harmonic increases only by less than the expected 6dB, whereas the 3rd-harmonic increases by less than the expected 12dB. This also shows up in the two-tone, 3rd-order intermodulation spurious (IM3) response curves. The 3rd-order spurious levels are extremely low at low output power levels. The output stage continues to hold them low even as the fundamental power reaches very high levels. As the Typical show, Characteristics the spurious intermodulation powers do not increase as predicted by a traditional intercept model. As the fundamental power level increases, the dynamic range does not decrease significantly. For two tones centered at 20MHz, with 4dBm/tone into a matched 50Ω load (that is,  $1V_{PP}$  for each tone at the load, which requires 4V<sub>PP</sub> for the overall 2-tone envelope at the output pin), the Typical Characteristics show a 82dBc difference between the test-tone power and the 3rd-order intermodulation spurious levels.

### NOISE PERFORMANCE

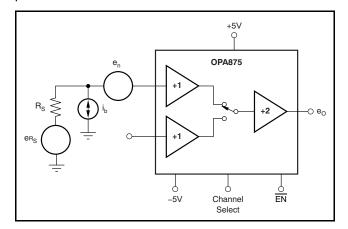

The OPA875 offers an excellent balance between voltage and current noise terms to achieve low output noise. As long as the AC source impedance looking out of the noninverting node is less than  $100\Omega$ , this current noise will not contribute significantly to the total output noise. The device input voltage noise and the input current noise terms combine to give low output noise under a wide variety of operating conditions. Figure 30 shows this device noise analysis model with all the noise terms included. In this model, all noise terms are taken to be noise voltage or current density terms in either nV/ $\sqrt{Hz}$  or pA/ $\sqrt{Hz}$ .

Figure 30. Noise Model

The total output spot noise voltage can be computed as the square root of the sum of all squared output noise voltage contributors. Equation 6 shows the general form for the output noise voltage using the terms shown in Figure 30.

$$e_{o} = 2\sqrt{e_{n}^{2} + (i_{b}R_{S})^{2} + 4kTR_{S}}$$

(6)

(5)

Dividing this expression by the device gain (2V/V) gives the equivalent input-referred spot noise voltage at the noninverting input as shown in Equation 7.

$$e_{n} = \sqrt{e_{n}^{2} + (i_{b}R_{S})^{2} + 4kTR_{S}}$$

(7)

Evaluating these two equations for the OPA875 circuit and component values shown in Figure 30 gives a total output spot noise voltage of 13.6nV/ $\sqrt{Hz}$  and a total equivalent input spot noise voltage of 6.8nV/ $\sqrt{Hz}$ . This total input-referred spot noise voltage is higher than the 6.7nV/ $\sqrt{Hz}$  specification for the mux voltage noise alone. This number reflects the noise added to the output by the bias current noise times the source resistor.

### THERMAL ANALYSIS

Heatsinking or forced airflow may be required under extreme operating conditions. Maximum desired junction temperature will set the maximum allowed internal power dissipation as discussed in this document. In no case should the maximum junction temperature be allowed to exceed +150°C.

Operating junction temperature (T<sub>J</sub>) is given by T<sub>A</sub> + P<sub>D</sub> ×  $\theta_{JA}$ . The total internal power dissipation (P<sub>D</sub>) is the sum of quiescent power (P<sub>DQ</sub>) and additional power dissipated in the output stage (P<sub>DL</sub>) to deliver load power. Quiescent power is simply the specified no-load supply current times the total supply voltage across the part. P<sub>DL</sub> depends on the required output signal and load but, for a grounded resistive load, be at a maximum when the output is fixed at a voltage equal to 1/2 of either supply voltage (for equal bipolar supplies). Under this condition P<sub>DL</sub> = V<sub>S</sub><sup>2</sup>/(4 × R<sub>L</sub>), where R<sub>1</sub> includes feedback network loading.

Note that it is the power in the output stage and not in the load that determines internal power dissipation.

As a worst-case example, compute the maximum  $T_J$  using an OPA875IDGK in the circuit of Figure 30 operating at the maximum specified ambient temperature of +85°C with its outputs driving a grounded 100 $\Omega$  load to +2.5V:

$P_{D} = 10V \times 11mA + (5^{2}[4 \times (100\Omega || 804\Omega)]) = 180mW$ Maximum T<sub>1</sub> = +85°C + (0.18mW × 140°C/W) = 110°C

This worst-case condition does not exceed the maximum junction temperature. Normally, this extreme case is not encountered. Careful attention to internal power dissipation is required.

SBOS340C-DECEMBER 2006-REVISED AUGUST 2008

### **BOARD LAYOUT GUIDELINES**

Achieving optimum performance with a high frequency amplifier such as the OPA875 requires careful attention to board layout parasitics and external component types. Recommendations that will optimize performance include:

a) Minimize parasitic capacitance to any AC ground for all of the signal I/O pins. Parasitic capacitance on the output pin can cause instability: on the noninverting input, it can react with the source impedance to cause unintentional bandlimiting. To reduce unwanted capacitance, a window around the signal I/O pins should be opened in all of the ground and power planes around those pins. Otherwise, ground and power planes should be unbroken elsewhere on the board.

b) Minimize the distance (< 0.25") from the power-supply pins to high frequency 0.1µF decoupling capacitors. At the device pins, the ground and power plane layout should not be in close proximity to the signal I/O pins. Avoid narrow power and ground traces to minimize inductance between the pins and the decoupling capacitors. The power-supply connections (on pins 9, 11, 13, and 15) should always be decoupled with these capacitors. An optional supply decoupling capacitor across the two power supplies (for bipolar operation) will improve 2nd-harmonic distortion performance. Larger (2.2µF to 6.8µF) decoupling capacitors, effective at lower frequency, should also be used on the main supply pins. These may be placed somewhat farther from the device and may be shared among several devices in the same area of the PCB.

c) Careful selection and placement of external components will preserve the high-frequency performance of the OPA875. Resistors should be a very low reactance type. Surface-mount resistors work best and allow a tighter overall layout. Metal-film and carbon composition, axially leaded resistors can also provide good high-frequency performance. Again, keep the leads and PCB trace length as short as possible. Never use wirewound type resistors in a high-frequency application. Other network components, such as noninverting input termination resistors, should also be placed close to the package.

d) Connections to other wideband devices on the board may be made with short direct traces or through onboard transmission lines. For short connections, consider the trace and the input to the next device as a lumped capacitive load. Relatively wide traces (50mils to 100mils) should be used, preferably with ground and power planes opened up around them.

### SBOS340C-DECEMBER 2006-REVISED AUGUST 2008

Estimate the total capacitive load and set R<sub>S</sub> from the plot of Figure 5. Low parasitic capacitive loads (< 5pF) may not need an R<sub>S</sub> because the OPA875 is nominally compensated to operate with a 2pF parasitic load. If a long trace is required, and the 6dB signal loss intrinsic to a doubly-terminated transmission line is acceptable, implement a matched impedance transmission line using microstrip or stripline techniques (consult an ECL design handbook for microstrip and stripline layout techniques). A 50 $\Omega$ environment is normally not necessary on board, and in fact, a higher impedance environment will improve distortion as shown in the Distortion versus Load plots. With a characteristic board trace impedance defined based on board material and trace dimensions, a matching series resistor into the trace from the output of the OPA875 is used as well as a terminating shunt resistor at the input of the destination device. Remember also that the terminating impedance will be the parallel combination of the shunt resistor and the input impedance of the destination device; this total effective impedance should be set to match the trace impedance. The high output voltage and current capability of the OPA875 allows multiple destination devices to be handled as separate transmission lines, each with their own series and shunt terminations. If the 6dB attenuation of a doubly-terminated transmission line is unacceptable, a long trace can be seriesterminated at the source end only. Treat the trace as a capacitive load in this case and set the series resistor value as shown in Figure 5. This will not preserve signal integrity as well as a doubly-terminated line. If the input impedance of the destination device is low, there will be some signal attenuation due to the voltage divider formed by the series output into the terminating impedance.

e) Socketing a high-speed part like the OPA875 is not recommended. The additional lead length and pin-to-pin capacitance introduced by the socket can create an extremely troublesome parasitic network which can make it almost impossible to achieve a smooth, stable frequency response. Best results are obtained by soldering the OPA875 onto the board.

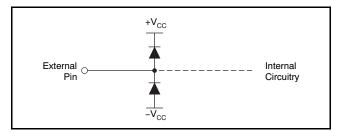

### INPUT AND ESD PROTECTION

The OPA875 is built using a very high-speed complementary bipolar process. The internal junction breakdown voltages are relatively low for these very small geometry devices. These breakdowns are reflected in the Absolute Maximum Ratings table. All device pins have limited ESD protection using internal diodes to the power supplies as shown in Figure 31.

Figure 31. Internal ESD Protection

These diodes provide moderate protection to input overdrive voltages above the supplies as well. The protection diodes can typically support 30mA continuous current. Where higher currents are possible (for example, in systems with  $\pm 15V$  supply parts driving into the OPA875), current-limiting series resistors should be added into the two inputs. Keep these resistor values as low as possible because high values degrade both noise performance and frequency response.

## **Revision History**

| Cł | nanges from Revision B (September 2007) to Revision C                                                              | Page |

|----|--------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed storage temperature range rating in Absolute Maximum Ratings table from –40°C to +125°C to –65°C to +125°C | 2    |

| Cł | nanges from Revision A (August 2007) to Revision B                                                                 | Page |

| •  | Changed ordering information column in Table 3                                                                     | 11   |

## PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | •    | Eco Plan     | Lead finish/       | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|------|--------------|--------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)          | Ball material      | (3)                 |              | (4/5)          |         |

|                  |        |              |         |      |      |              | (6)                |                     |              |                |         |

| OPA875ID         | ACTIVE | SOIC         | D       | 8    | 75   | RoHS & Green | NIPDAU             | Level-2-260C-1 YEAR | -40 to 85    | OPA875         | Samples |

| OPA875IDG4       | ACTIVE | SOIC         | D       | 8    | 75   | TBD          | Call TI            | Call TI             | -40 to 85    |                | Samples |

| OPA875IDGKR      | ACTIVE | VSSOP        | DGK     | 8    | 2500 | RoHS & Green | NIPDAU   NIPDAUAG  | Level-2-260C-1 YEAR | -40 to 85    | BPL            | Samples |

| OPA875IDGKT      | ACTIVE | VSSOP        | DGK     | 8    | 250  | RoHS & Green | Call TI   NIPDAUAG | Level-2-260C-1 YEAR | -40 to 85    | BPL            | Samples |

| OPA875IDGKTG4    | ACTIVE | VSSOP        | DGK     | 8    | 250  | TBD          | Call TI            | Call TI             | -40 to 85    |                | Samples |

| OPA875IDR        | ACTIVE | SOIC         | D       | 8    | 2500 | RoHS & Green | NIPDAU             | Level-2-260C-1 YEAR | -40 to 85    | OPA875         | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

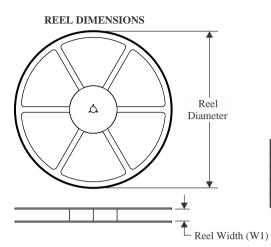

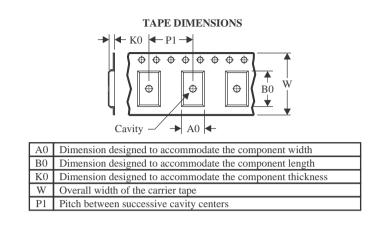

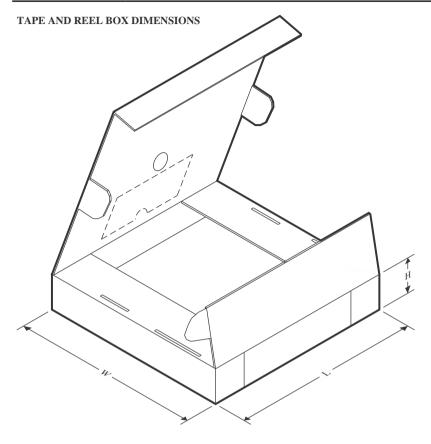

## TAPE AND REEL INFORMATION

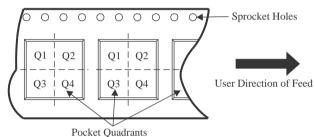

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *A | Il dimensions are nominal |       |                    |   |      |                          |                          |            |            |            |            |           |                  |

|----|---------------------------|-------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

|    | Device                    | •     | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|    | OPA875IDGKR               | VSSOP | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

|    | OPA875IDR                 | SOIC  | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

# PACKAGE MATERIALS INFORMATION

2-Nov-2023

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA875IDGKR | VSSOP        | DGK             | 8    | 2500 | 356.0       | 356.0      | 35.0        |

| OPA875IDR   | SOIC         | D               | 8    | 2500 | 356.0       | 356.0      | 35.0        |

## TEXAS INSTRUMENTS

www.ti.com

2-Nov-2023

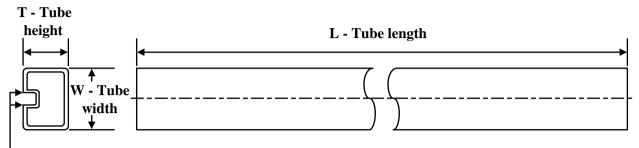

## TUBE

## - B - Alignment groove width

\*All dimensions are nominal

| Device   | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|----------|--------------|--------------|------|-----|--------|--------|--------|--------|

| OPA875ID | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

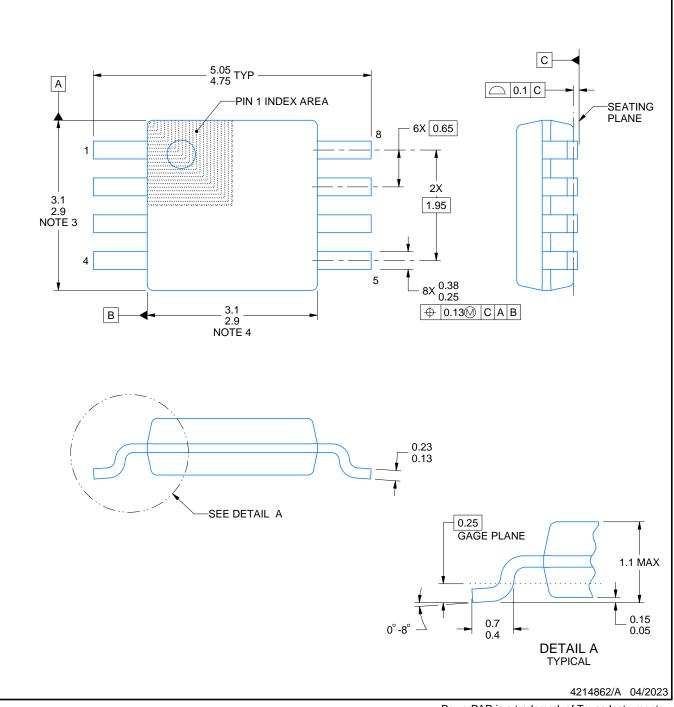

# **DGK0008A**

# **PACKAGE OUTLINE**

# VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

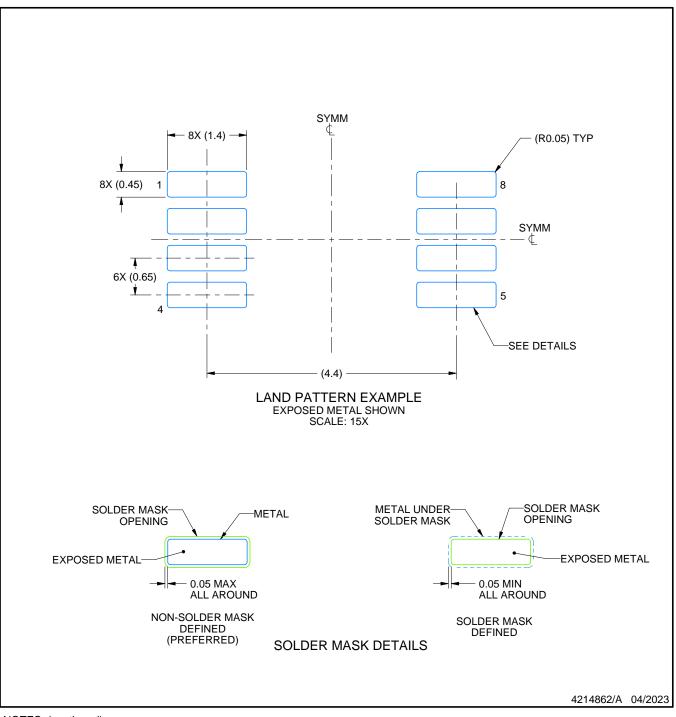

# DGK0008A

# **EXAMPLE BOARD LAYOUT**

# <sup>™</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown

- on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

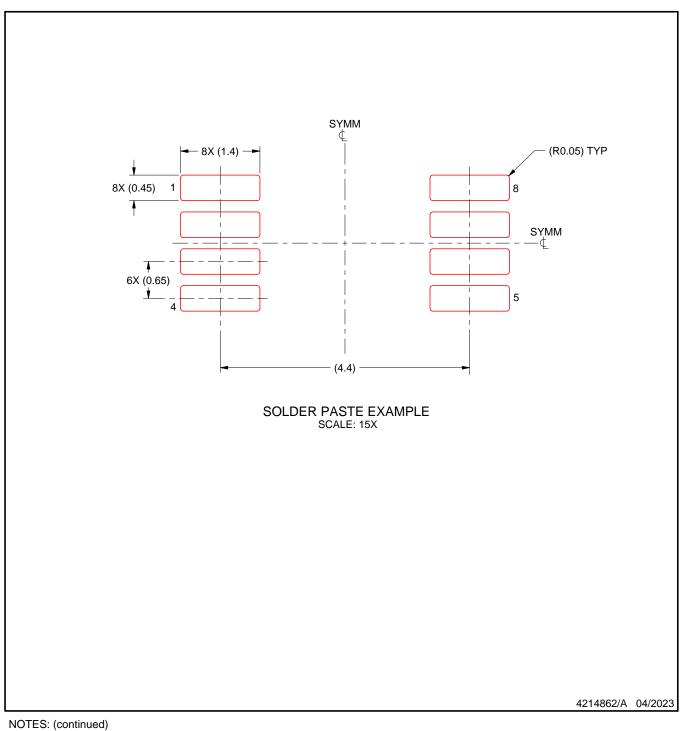

# DGK0008A

# **EXAMPLE STENCIL DESIGN**

# <sup>™</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

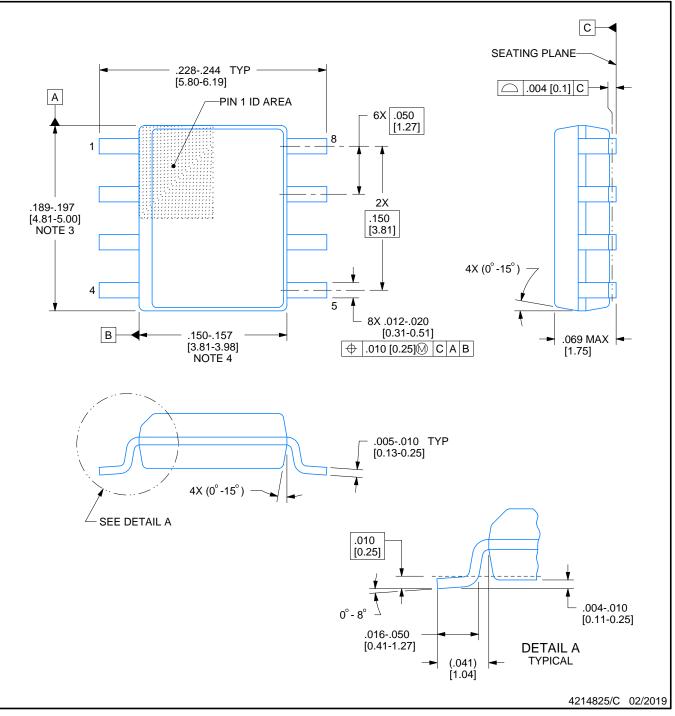

# D0008A

# **PACKAGE OUTLINE**

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

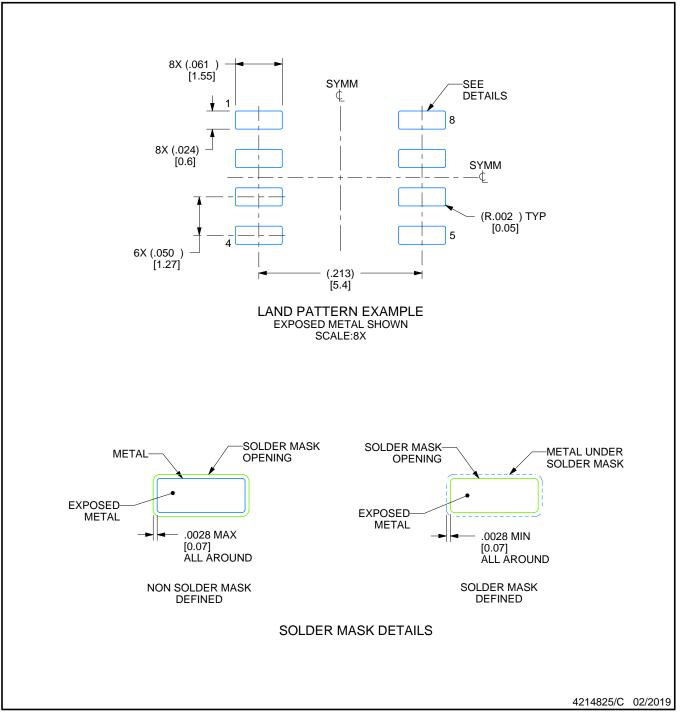

# D0008A

# **EXAMPLE BOARD LAYOUT**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

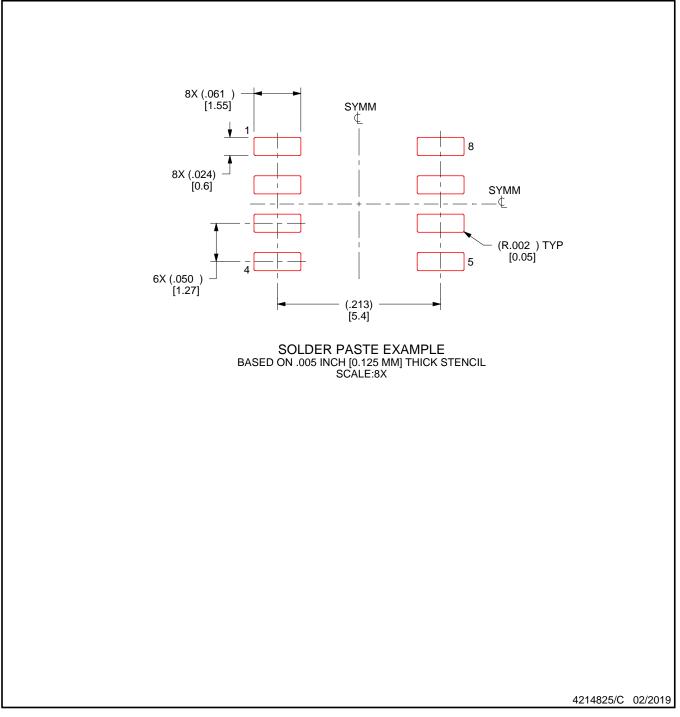

# D0008A

# **EXAMPLE STENCIL DESIGN**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated