## **LP2995**

LP2995 DDR Termination Regulator

Literature Number: JAJSA05

2006年6月

## LP2995

## DDR ターミネーション・レギュレータ

#### 概要

LP2995 は JEDEC 標準の SSTL-2、SSTL-3 仕様に適合する、DDR-SDRAM ターミネーションのリニア・レギュレータです。 LP2995 は負荷変動に対して優れた応答を発揮する高速オペアンプを内蔵しています。 出力段は 1.5A の連続電流を供給でき、さらに DDR-SDRAM ターミネーションに求められる最大 3A の変動ピークにも対応していますが、貫通電流は発生しません。  $V_{SENSE}$  端子を介した電圧監視により優れた出力負荷レギュレーションを実現するとともに、チップセットや DDR DIMM に必要な  $V_{REF}$  電圧も生成して出力します。

#### 特許出願中

## 特長

低出力電圧オフセット + 5V、 + 3.3V または + 2.5V 電源で動作 電流ソースおよび電流シンク 少ない外付け部品 外付け抵抗不要 リニア・トポロジー SO-8、PSOP-8、LLP-16 パッケージで供給 低コストで設計が容易

#### アプリケーション

DDR ターミネーション電圧生成 SSTL-2 SSTL-3

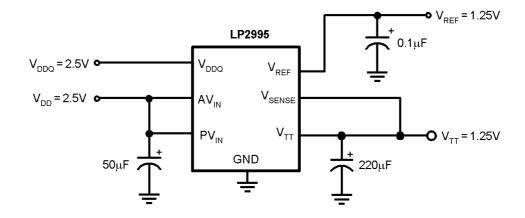

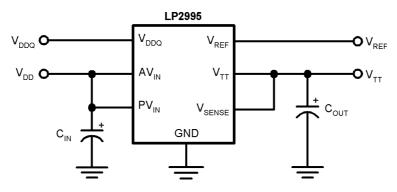

## 代表的なアプリケーション回路

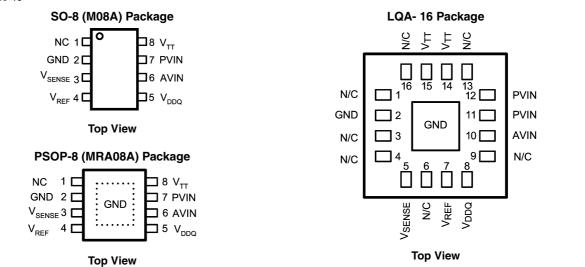

## 端子説明

## 端子説明

| SO-8 ピン、<br>PSOP-8 ピン | LLP ピン                | 端子名                | 機能                                          |  |

|-----------------------|-----------------------|--------------------|---------------------------------------------|--|

| 1                     | 1, 3, 4, 6, 9, 13, 16 | NC                 | 内部接続なし。 スルーホールを配置可能                         |  |

| 2                     | 2                     | GND                | グラウンド                                       |  |

| 3                     | 5                     | V <sub>SENSE</sub> | レギュレートされた V <sub>TT</sub> の電圧フィードバック入力端子    |  |

| 4                     | 7                     | $V_{REF}$          | 内部リファレンス電圧 V <sub>DDQ</sub> /2 のバッファ出力      |  |

| 5                     | 8                     | $V_{\mathrm{DDQ}}$ | 内部リファレンス電圧 V <sub>DDQ</sub> /2 を生成するための入力電圧 |  |

| 6                     | 10                    | $AV_{IN}$          | 内部制御回路電源入力端子                                |  |

| 7                     | 11, 12                | $PV_{IN}$          | パワー・オペアンプ出力段専用電源入力端子                        |  |

| 8                     | 14、15                 | V <sub>TT</sub>    | ターミネーション抵抗に接続するターミネーション電圧出力                 |  |

|                       | EP                    | EP                 | 放熱用パッドです。グラウンドに接続してください。                    |  |

## 製品情報

| Order Number     | Package Type | NSC Package<br>Drawing | Supplied As              |  |

|------------------|--------------|------------------------|--------------------------|--|

| LP2995M          | SO-8         | M08A                   | 95 Units per Rail        |  |

| LP2995MX         | SO-8         | M08A                   | 2500 Units Tape and Reel |  |

| LP2995MR         | PSOP-8       | MRA08A                 | 95 Units per Rail        |  |

| LP2995MRX PSOP-8 |              | MRA08A                 | 2500 Units Tape and Reel |  |

| LP2995LQ         | LLP-16       | LQA16A                 | 1000 Units Tape and Reel |  |

| LP2995LQX LLP-16 |              | LQA16A                 | 4500 Units Tape and Reel |  |

$2.2V \sim AV_{IN}$

#### 絶対最大定格 (Note 1)

本データシートには軍用・航空宇宙用の規格は記載されていません。 関連する電気的信頼性試験方法の規格を参照ください。

リード温度(ハンダ付け、10秒間) 260 ESD 耐圧 (Note 7) 1kV

$-0.3V \sim +6V$ GND 基準の PV<sub>IN</sub>、AV<sub>IN</sub>、V<sub>DDO</sub> 各電圧

保存温度範囲 - 65 ~ + 150 接合部温度

150 接合部温度範囲 (Note 5) 0 ~ + 125 43 /W GND 基準の AV<sub>IN</sub> 電圧  $2.2V \sim 5.5V$ GND 基準の PV<sub>IN</sub> 電圧

PSOP-8 熱抵抗(<sub>IA</sub>) SO-8 熱抵抗 ( <sub>JA</sub>) 151 /W LLP-16 熱抵抗 ( <sub>IA</sub>) 51 /W

### 電気的特性

標準字体で記載された仕様は  $T_J$  = 25 の場合であり、太字で記載されたリミット値は「動作温度範囲」 $(T_J$  = 0 C ~ + 125 C) に 適用されます。 特記のない限り、 $AV_{IN}$  =  $PV_{IN}$  = 2.5V、 $V_{DDO}$  = 2.5V です (Note 6)。

動作定格

| Symbol                 | Parameter                             | Conditions                      | Min  | Тур   | Max  | Units |

|------------------------|---------------------------------------|---------------------------------|------|-------|------|-------|

| $V_{REF}$              | V <sub>REF</sub> Voltage              | I <sub>REF_OUT</sub> = 0mA      | 1.21 | 1.235 | 1.26 | V     |

| VOS <sub>VTT</sub>     | V <sub>TT</sub> Output Voltage Offset | I <sub>OUT</sub> = 0A           | -15  | 0     | 15   | mV    |

|                        |                                       | (Note 2)                        | -20  |       | 20   |       |

| $\Delta V_{TT}/V_{TT}$ | Load Regulation (Note 3)              | I <sub>OUT</sub> = 0 to 1.5A    |      | 0.5   |      | %     |

|                        |                                       | I <sub>OUT</sub> = 0 to -1.5A   |      | -0.5  |      |       |

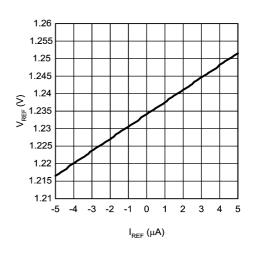

| Z <sub>VREF</sub>      | V <sub>REF</sub> Output Impedance     | I <sub>REF</sub> = -5μA to +5μA |      | 5     |      | kΩ    |

| Z <sub>VDDQ</sub>      | VDDQ Input Impedance                  |                                 |      | 100   |      | kΩ    |

| l <sub>q</sub>         | Quiescent Current                     | I <sub>OUT</sub> = 0A           |      | 250   | 400  | μA    |

| <sup>-</sup> 4         | Janes Sanon                           | (Note 4)                        |      | 250   | 400  |       |

Note 1: 「絶対最大定格」とは、デバイスが破壊する可能性のあるリミット値をいいます。「動作定格」とはデバイスが正しく機能する条件を示しますが、特定の 性能限界を保証するものでありません。保証された仕様、そのテスト条件については「電気的特性」を参照してください。仕様の保証は、表記のテス ト条件にのみ適用されます。記載のテスト条件以外でデバイスを動作させると、性能特性が低下することがあります。

Note 2:  $V_{TT}$  オフセットは、 $V_{REF}$  -  $V_{TT}$  として定義される電圧測定です。

Note 3: ロード・レギュレーションは 10 ms の電流パルスを用いて  $V_{TT}$  を測定しテストされています。

待機時消費電流は  $\mathrm{AV}_{\mathrm{IN}}$  に流れ込む電流として定義されています。

Note 5: 高温では、熱抵抗に基づいてデバイスをディレーティングする必要があります。 SO-8 パッケージでは、ヒートシンクなしで接合部から周囲への熱抵抗  $_{

m JA}$  = 151  $_{

m /W}$  でディレーティングしてください。 LLP-16 では、接合部から周囲への熱抵抗  $_{

m JA}$  = 51  $_{

m /W}$  でディレーティングしてください。

Note 6: 25 時のリミ外値は 100%テストされます。 全動作温度範囲におけるリミ外値は、統計的品質管理 (SQC) 方式によって決められた補正データを加味し て保証されています。これらのリミット値は、ナショナルセミコンダクター社の平均出荷品質レベル(AOQL)の計算に使用されます。

Note 7: 使用したテスト回路は人体モデルに基づき、100pFのコンデンサから直列抵抗 1.5k を通して各端子に放電させます。

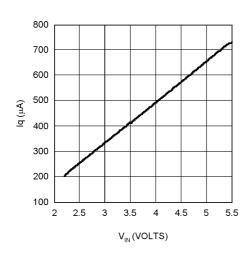

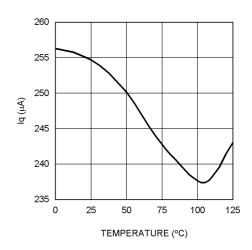

## 代表的な性能特性

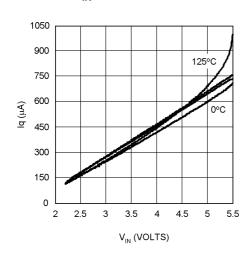

Iq vs V<sub>IN</sub> (25 )

Iq vs Temperature ( $V_{IN} = 2.5V$ )

Iq vs V<sub>IN</sub> (0, 25, 85, and 125 )

V<sub>REF</sub> vs I<sub>REF</sub>

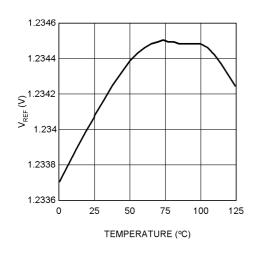

**V<sub>REF</sub> vs Temperature (No Load)**

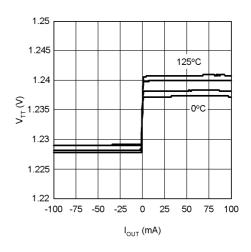

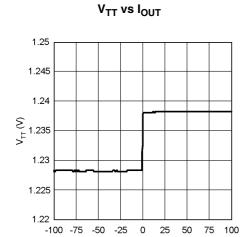

V<sub>TT</sub> vs I<sub>OUT</sub> (0, 25, 85, and 125 )

## 代表的な性能特性(つづき)

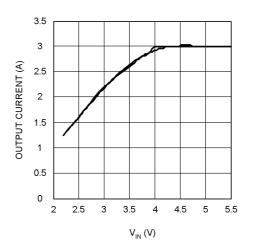

# Maximum Output Current (Sourcing) vs $V_{IN}$ (VDDQ = 2.5)

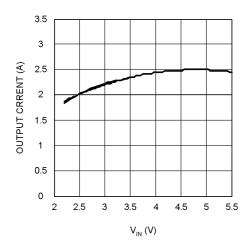

# Maximum Output Current (Sinking) vs $V_{IN}$ (VDDQ = 2.5)

I<sub>OUT</sub> (mA)

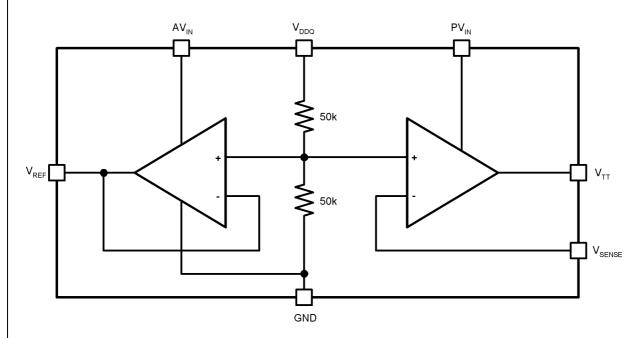

#### ブロック図

#### 説明

LP2995 は JEDEC 標準の SSTL-2、SSTL-3 仕様に適合する、DDR-SDRAM バス・ターミネーションのリニア・レギュレータです。 LP2995 の  $V_{TT}$  出力は  $V_{DDQ}/2$  に等しくなるようにレギュレートされ、電流ソースや電流シンクに対応しています。  $V_{REF}$  端子はリファレンス電圧 $V_{DDQ}/2$ のバッファ出力となっており、DDR-SDRAM およびノース・ブリッジ・チップセット(メモリ・コントローラ)に共通リファレンス電圧を与えます。  $V_{TT}$  電圧は、全電流範囲で  $V_{REF}$  電圧に忠実に追従し、かつ出力段で貫通電流の発生を防いでいます。

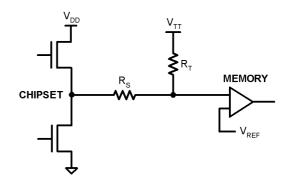

シリーズ・スタブ・ターミネーテッド・ロジック (SSTL) は、メモリバスのデータ転送時の信号品質を改善するために開発されました。このターミネーション方式は、高い周波数で DDR RAM のデータ転送を行う際に、信号反射によるデータエラーを防ぐためには不可欠と言えます。 最も一般的なターミネーション回路形式は、チップセットとメモリの間に 1 つの直列抵抗  $R_S$  を設け、さらにターミネーション抵抗  $R_T$  を 1 つ用いる、Class II シグナル・パラレル・ターミネーションです。 回路の例を Figure 1 に示します。

FIGURE 1.

#### 端子説明

#### AV<sub>IN</sub> および PV<sub>IN</sub>

$AV_{IN}$  および  $PV_{IN}$  は LP2995 の電源端子です。  $AV_{IN}$  は、全内部回路、2 つのオペアンプ、 $V_{REF}$  出力段の電源として用いられます。  $PV_{IN}$  は、 $V_{TT}$  生成用パワー・オペアンプの出力段専用電源です。 SSTL-2 アプリケーションでは、 $AV_{IN}$  と  $PV_{IN}$  端子をともに 2.5V 電源に接続すると、最適な性能が得られます。 短絡により 2 つの端子を個別にバイパスする必要はありません。

#### VDDO

$V_{DDQ}$  は入力で、 $V_{TT}$  と $V_{REF}$  のレギュレートに必要な内部リファレンス電圧の生成に使われます。内部リファレンス電圧は、2 つの 50k 内蔵抵抗よって $V_{DDQ}$ を分圧して作られます。これによって、 $V_{TT}$ と $V_{REF}$ の $V_{DDQ}$ /2に対する正確な追従が得られます。DIMM またはチップセットの  $V_{DDQ}$  電源に対して、リモート・センスとなるように  $V_{DDQ}$  端子に配線してください。具体的には DIMM 用 2.5 V 電源を  $V_{DDQ}$  端子に直接接続します。こうすると内部リファレンス電圧は、電源配線での電圧降下の影響を受けずに、DDR メモリ部の電源電圧に正確に追従します。SSTL-2 アプリケーションで  $V_{DDQ}$  は 2.5 V なので、リファレンス電圧  $V_{REF}$  およびターミネーション電圧  $V_{TT}$  として 1.25 V が生成されます。 一方 SSTL-3 アプリケーションでは、0.5 以外の係数を用いて内部リファレンス電圧を生成することが望ましい場合があります。たとえば、よく用いられているリファレンス電圧は、 $V_{DDQ}$  × 0.45 です。 $V_{DDQ}$  端子に直列抵抗を挿入し内蔵抵抗との抵抗分圧比を変更すると係数を変えられます。

#### VCENCE

本センス端子の目的は、遠端のロード・レギュレーションの改善にあります。多くのマザーボードでは、V<sub>TT</sub> は長い配線を通ってターミネーション抵抗に接続されます。このとき LP2995 の出力点で電圧のセンスを行うと、長い配線によって起こる大きな電圧降下により、バス端のターミネーション電圧はバスの他点よりも低くなってしまう問題が生じます。 そこでバスの中点付近の電圧を V<sub>SENSE</sub> 端子に与え、バス遠端で電圧が低下する問題を改善するようにしてください。この方法によりバス全体の電圧が良好に保たれます。

Note: 遠端でのロード・レギュレーションを行わない場合は、 $V_{SENSE}$  端子には  $V_{TT}$  を与えなければなほせん。

#### VDEE

$V_{REF}$  は内部リファレンス電圧  $V_{DDQ}/2$  のバッファ出力です。本出力は、ノースプリッジ・チップセットとメモリに対するリファレンス電圧として使用します。通常それらの入力のインピーダンスは高いので、 $V_{REF}$  端子を流れる電流はわずかです。 ノイズ対策として端子近くにバイパス・コンデンサを設けると、レギュレーション性能が改善されます。 推奨品は  $0.1\,\mu F$  のセラミック・コンデンサです。

#### ٧--

VTTはバスのターミネーション抵抗に与えられるレギュレート電圧出 力です。 V<sub>DDO</sub>/2 電圧に高い精度で追従し、併せて電流ソース と電流シンクの能力を備えています。LP2995は、高速応答によっ て最大±3Aまでのピーク電流変動に対応できるように設計されて の "Maximum Output Current" グラフに記載されています。 最大 連続電流定格を超える変動が長時間にわたり見込まれるのであ れば、出力コンデンサ容量を十分大きくして過度の電圧低下の発 生を防いでください。LP2995 は出力電流の大きな変動にも耐え 得るように設計されていますが、すべての条件のもとで、そのよう な状況に長時間対応するのは困難です。その理由は、小型の 標準パッケージを採用しているため、過大な内部電力損失によっ て生じる熱を逃がせないためです。 長時間にわたり大電流が求 められる場合は、最大接合部温度を超えないように注意が必要 です。熱に応じて、使用定格を適切に下げるようにしてください (「放熱」の項を参照)。

#### 部品の選択

#### 入力コンデンサ

LP2995 は、入力安定化を目的とする入力コンデンサは必要ではありません。ただし大きな負荷変動時に入力電圧の低下を防ぐために、入力コンデンサの使用を推奨します。 入力コンデンサは、可能な限り PV<sub>IN</sub> の近くに配置します。 アプリケーションの要件によって推奨条件が異なります。 アルミ電解コンデンサを用いた場合、推奨容量は 50μF です。 セラミック・コンデンサを用いる場合は、容量は 10μF 前後とし、誘電体の温度特性が X5R 以上のコンデンサが理想的といえます。 なお、LP2955 が 2.5V DC/DC コンバータの出力コンデンサの近くにレイアウトされている場合は、入力コンデンサを省略しても構いません。

#### 出力コンデンサ

LP2995 は、出力コンデンサの容量と ESR (等価直列抵抗)に依存しないよう設計されています。そのため柔軟にコンデンサを選択できます。出力コンデンサは、アプリケーションと負荷変動に対する V<sub>TT</sub> の応答要求に基づいて決めてください。DDR-SDRAMを用いた SSTL アプリケーションでは、100 μF 以上の低 ESR コンデンサを一般的に推奨します。このうち ESR は、見込まれる最大電流スパイクと、許容される出力電圧低下から決定してください。入手可能なコンデンサ類のうち、代表的な品種について次に説明します。

AL - アルミ電解コンデンサは 120Hz におけるインピーダンスのみを規定している点に注意が必要で、これは高い周波数領域では特性が劣ることを示しています。LP2995 回路にアルミ電解コンデンサを適用できる条件は、20kHz ~ 100kHz の高い周波数領域でもインピーダンスが規定されている場合に限られます。アルミ電解コンデンサを複数個並列に接続すると総ESRを下げられます。ただし問題点はESRが温度により変化すれば、低温になるとESRが急激に増大します。

セラミック・セラミック・コンデンサは、一般的に容量は 10μF ~ 100μF と大きくありませんが、ESR が極めて小さい (通常 10m以下)ため、優れたノイズ・バイパス特性を備えています。しかし使用している誘電体の種類よっては、電圧と温度に対して充分な特性を備えていない 他のも存在します。一般的に容量が小さいといった理由により、セラミック・コンデンサはアルミ電解コンデンサなどに並列接続しての使用を推奨します。また使用するすべてのセラミック・コンデンサには、誘電体の温度特性が X5R 以上の品種を推奨します。

化合物 - OS-CON(有機半導体)やSP(機能性高分子)のような化合物を用いたコンデンサが、数社からリリースされています。これらのコンデンサは低ESRを維持しながら大きな容量を実現しています。他のコンデンサに比べてコストは高くなりますが、実サイズと性能が重要な場合に最適なソリューションといえます

#### 放熱

LP2995 はリニア・レギュレータなので、熱の原因となる内部消費電力が  $V_{TT}$  電流によって発生します。デバイスを損壊から守るには最大許容接合部温度を超えてはならないので、見込まれる最大周囲温度と消費電力にもとづき、デバイスを定格以下で動作させるよう注意を払う必要があります。最大許容内部温度上昇  $(T_{Rmax})$  は、アプリケーションで与えられる最大周囲温度  $(T_{Amax})$  と、最大許容接合部温度  $(T_{Jmax})$  から求められます。

$$T_{Rmax} = T_{Jmax} - T_{Amax}$$

この式から、デバイスの最大消費電力 ( $P_{\mathrm{Dmax}}$ ) は次式で示されます。

$$P_{Dmax} = T_{Rmax} / J_A$$

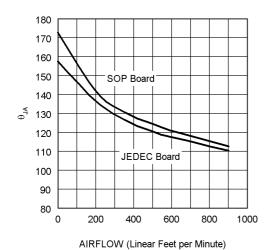

LP2995 の  $_{\rm JA}$  は、使用しているパッケージ、プリント基板の銅箔 厚み、スルーホールの数、エアフローで決まります。 たとえば SO-8 パッケージを、標準的な  $203\times102{\rm mm}$ 、銅箔厚み  $35\,\mu{\rm m}$  の基板に実装し、エアフローなしの室温で  $0.5{\rm W}$  を消費させた場合の  $_{\rm JA}$  は、163 /W です。また JEDEC スタンダードの  $76\times102{\rm mm}$ 、70  $\mu{\rm m}$  厚銅箔の基板を用いると、  $_{\rm JA}$  は 151.2 /W に低下します。 Figure 2 に上記 2 つの基板における、エアフローに対する  $_{\rm JA}$  の変化を示します。

FIGURE 2. JA vs Airflow (SO-8)

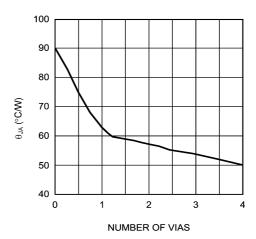

LLP パッケージの出力電流を最大限に引き出す上で、基板レイアウトも極めて重要です。 DAP 直下に単純にスルーホールを打つだけでも、  $_{\rm JA}$ を大幅に低下できます。 Figure 3 は、 $18\,\mu{\rm m}/35\,\mu{\rm m}/35\,\mu{\rm m}/18\,\mu{\rm m}$  の銅箔で構成される 4 層 JEDEC 基板に実装した場合の LLP パッケージの熱特性です。 スルーホールを間隔 1.27mm で最大 4 つに増やした時、50.41 /W の  $_{\rm JA}$  が得られます。 このグラフにおけるスルーホールのメッキ厚は  $36\,\mu{\rm m}$  です。

FIGURE 3. LLP-16 JA vs # of Vias (4 Layer JEDEC Board))

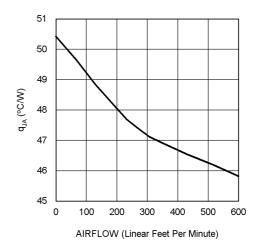

パッケージに定常的なエアフローを与えても  $_{

m JA}$  は低下します。上記条件で  $2\times 2$  のスルーホール配列を用いた場合、エアフローによる  $_{

m JA}$  の低下を Figure 4 に示します。

FIGURE 4. JA vs Airflow Speed (JEDEC Board with 4 Vias)

### 代表的なアプリケーション回路

Figure 5 に、DDR-SDARM の SSTL-2 ターミネーション方法に用いられる代表的なアプリケーション回路を示します。

FIGURE 5. SSTL-2 Implementation

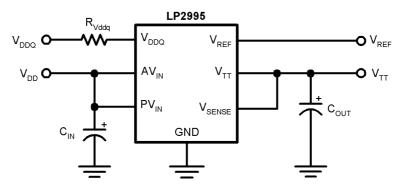

内蔵されている 2 つの 50k 抵抗の分圧により、 $V_{TT}$  出力は  $V_{DDQ}$  × 0.5 に等しくなります。一方 SSTL-3 アプリケーションまた はその他のアプリケーションでは、0.5 以外の係数を用いて内部リファレンス電圧を生成することが望ましい場合があります。 その場

合の回路を Figure 6 に示します。 $V_{\rm DDQ}$  端子に外部抵抗を直列に接続して、リファレンス電圧を下げられます。 たとえば 11.1k 抵抗を追加すると分圧比が変わるため内部リファレンス電圧が下が $\lambda_{\rm VT}$ と $V_{\rm REF}$ 出力は $V_{\rm DDQ}$  × 0.45 に追従するようになります。

FIGURE 6. SSTL-3 Implementation

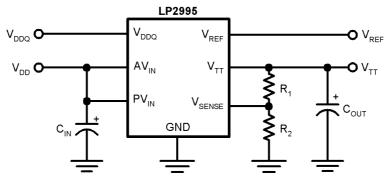

またアプリケーションによっては、逆に  $V_{TT}$  出力を  $V_{DDQ} \times 0.5$  より高くする必要があります。 その場合は抵抗分圧ネットワークを  $V_{TT}$ とGND間に挿入し $V_{SENSE}$ に分圧した電圧を与えると、 $V_{REF}$

電圧とは独立して  $V_{TT}$  電圧を高められます。 回路例を Figure 7 に示します。

FIGURE 7.

## プリント基板レイアウトの考慮事項

- 1. 最適な性能を得るために  $AV_{\rm IN}$  端子と  $PV_{\rm IN}$  端子同士は短絡してください。またパイパス・コンデンサを  $PV_{\rm IN}$  端子の可能な限り近くに配置してください。

- 2. GND 端子は、熱特性を高めるために、複数のスルーホール によってグラウンド・プレーンに接続してください。

- 3. V<sub>SENSE</sub> 端子には、V<sub>TT</sub>ターミネーションされるバスのレギュレーションが必要な点に接続してください。 マザーボード・アプリケーションではターミネーション・バスの中点が理想的です。

- 4. V<sub>DDQ</sub> 入力は、DIMM またはチップセットの V<sub>DDQ</sub> 電源に対してリモート・センスとなるように接続します。 内部リファレンス 電圧を最も精度高く生成できるようになります。

- 5. V<sub>REF</sub>にはレギュレーション性能の改善のため、0.1 μF ~ 0.01 μF のセラミック・コンデンサを接続してノイズをバイパスしてください。コンデンサは V<sub>REF</sub> 端子の可能な限り近くに配置してください。

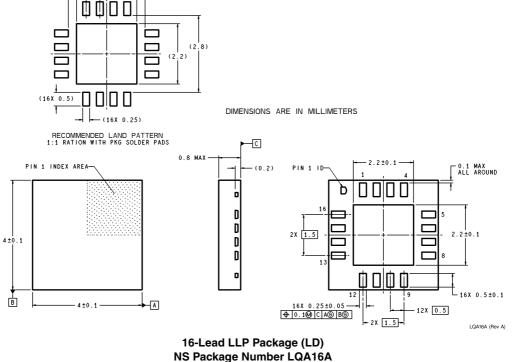

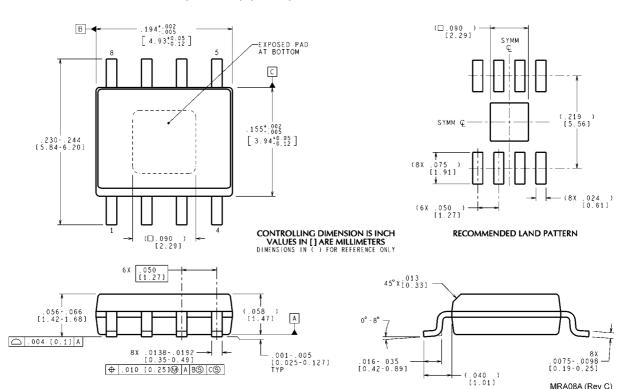

## 外形寸法図 単位は millimeters A-4.9±0.1 [.193±.004] NOT INCLUDING MOLD FLASH 0.15[.006] MAX PER END 6±0.2 [.236±.008] 6X (1.27 [.05] RECOMMENDED LAND PATTERN 1.35-1.75 [.053-.069] TYP R0.18±0.02 [.007±.0008] 45° X 0.25-0.50 [.010-.020] △ 0.1[.004] C C -SEATING PLANE (1.04) [.041] CONTROLLING DIMENSION IS MILLIMETER VALUES IN [ ] ARE INCHES DIMENSIONS IN ( ) FOR REFERENCE ONLY M08A (Rev K) 8-Lead Small Outline Package (M8) NS Package Number M08A (2.2) (12X 0.5) (16X 0.5) 0 010 0

## 外形寸法図 特記のない限り inches (millimeters) (つづき)

8-Lead PSOP Package (PSOP-8) NS Package Number MRA08A

このドキュメントの内容はナショナル セミコンダクター社製品の関連情報として提供されます。ナショナル セミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナル セミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が 課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナ ル セミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナル セミコンダクター社の部品 を使用した製品および製品適用の責任は購入者にあります。ナショナル セミコンダクター社の製品を用いたいかなる製品の使用ま たは供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナル セミコンダクター社との取引条件で規定される場合を除き、ナショナル セミコンダクター社は一切の義務を負わないものとし、また、ナショナル セミコンダクター社の製品の販売か使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または黙示的保証も行いません。

#### 生命維持装置への使用について

ナショナル セミコンダクター社の製品は、ナショナル セミコンダクター社の最高経営責任者 (CEO) および法務部門 (GENERAL COUNSEL) の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

ここで、生命維持装置またはシステムとは(a)体内に外科的に使用されることを意図されたもの、または(b)生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

National Semiconductor とナショナル セミコンダクターのロゴはナショナル セミコンダクター コーポレーションの登録商標です。その他のブランド や製品名は各権利所有者の商標または登録商標です。

Copyright © 2006 National Semiconductor Corporation

製品の最新情報については www.national.com をご覧ください。

#### ナショナル セミコンダクター ジャパン株式会社

本社 / 〒 135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

www.national.com/jpn/

## ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝擊

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上