LMK3H0102

JAJSS15 - NOVEMBER 2023

# LMK3H0102 リファレンスレス、2 差動または 5 シングルエンド出力、PCle Gen 1~6 準拠、プログラマブル BAW クロック ジェネレータ

# 1 特長

- BAW 共振器を内蔵、外部リファレンスは不要

- フレキシブルな周波数生成:

- 2 チャネル分圧器: 2.5MHz~400MHz の範囲 で最大3つの異なる出力周波数

- 最大 200MHz までの LVCMOS 出力をサポー ト: 1.8V、2.5V、または3.3V

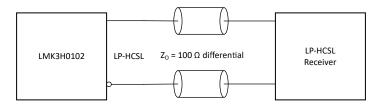

- OUT0 ピンおよび OUT1 ピン上で AC-LVDS、 DC-LVDS、LP-HCSL、LVCMOS の組み合わせ

- 追加の LVCMOS 出力により最大 5 つの LVCMOS クロックを生成可能

- 総出力周波数安定性:±25ppm

- 2 つの機能モード:I<sup>2</sup>C または事前にプログラムさ れた OTP

- 完全に構成可能な I<sup>2</sup>C アドレス

- 周囲温度:-40℃~85℃

- PCIe Gen 1~Gen 6 準拠:共通クロック (SSC、 SRNS、SRIS あり / なし)

- 非常に小さい PCIe ジッタ:

- PCle Gen 3 の共通クロックのジッタ: 140fs 以下 (PCIe の上限は 1ps)

- PCle Gen 4 の共通クロックのジッタ: 140fs 以下 (PCIe の上限は 500fs)

- PCIe Gen 5 の共通クロックのジッタ: 45fs 以 下 (PCIe の上限は 150fs)

- PCIe Gen 6 の共通クロックのジッタ: 45fs 以 下 (PCIe の上限は 100fs)

- SSC 出力モードと非 SSC 出力モードの混合をサ ポート、PCIe Gen 1~Gen 6 のすべてに準拠

- 2つの SSC 出力、2つの非 SSC 出力、または 1 つの SSC 出力と 1 つの非 SSC 出力

- プログラム可能な SSC 変調深度

- 事前プログラム済 み:-0.1%、-0.25%、-0.3%、および-0.5%の ダウン スプレッド

- 抵抗によるプログラミングが可能:-0.1% ~-3% のダウン スプレッド、または ±0.05% ~ ±1.5% のセンター スプレッド

- $VDD = VDDO = 1.8V/2.5V/3.3V \pm 5\%$

- 両方の出力が LP-HCSL の場合、消費電流が 60mA まで低下

- LP-HCSL 出力において、500kHz のスイッチング ノイズで -93.1dBc の PSNR を提供する内蔵 LDO

- スタートアップ時間:<5ms

- 出力間スキュー:<50ps

- フェイルセーフ 入力および VDD ピン

# 2 アプリケーション

• PCle Gen 1~Gen 6 のクロック生成

- サーバー・マザーボード

- NIC、SmartNIC

- ハードウェア・アクセラレータ

- PCIe SSD

- アドイン カード、PCIe 拡張カード

- 複合機 (マルチファンクション プリンタ)

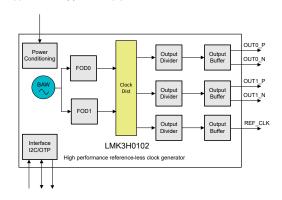

LMK3H0102 は、スペクトラム拡散クロック (SSC) をサポートする、2 出力 PCle Gen 1~Gen 6 準 拠のリファレンスレス クロック ジェネレータです。 このデバイスは、テキサス・インスツルメンツ独自の バルク弾性波 (BAW) 技術に基づいており、水晶振動 子や外部クロック リファレンスを用いずに、±25ppm のクロック出力を供給します。このデバイスは、2つ の SSC クロック、2 つの非 SSC クロック、また は 1 つの SSC クロックと 1 つの非 SSC クロック を同時に供給できます。このデバイスは、SSC あり または SSC なしの共通クロック、SRNS (Separate Reference No Spread), SRIS (Separate Reference Independent Spread) など、Gen 1 から Gen 6 までの PCIe に完全準拠しています。

このデバイスは、GPIO ピンや I2C インターフェイス を介して簡単に構成できます。デバイスへの電力供給 には、外付けの DC/DC 回路を使用できます。電源の フィルタ処理と DC/DC 回路からの電源供給に関する 詳細なガイドラインについては、「電源に関する推奨 事項」 を参照してください。

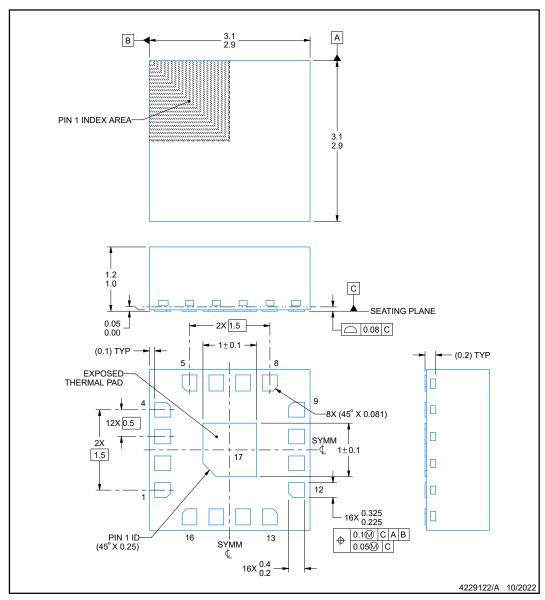

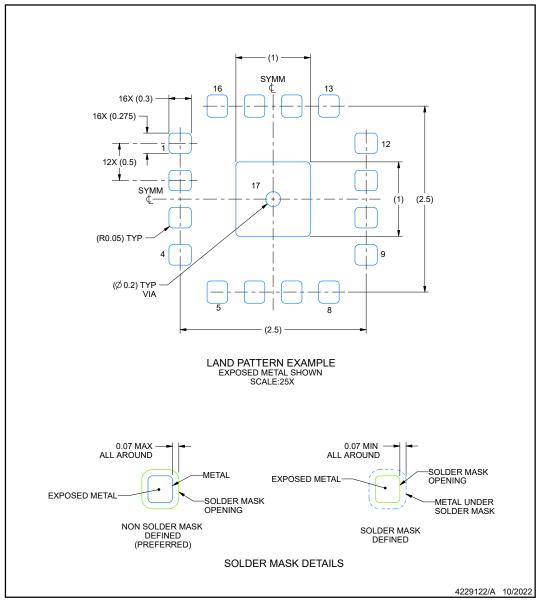

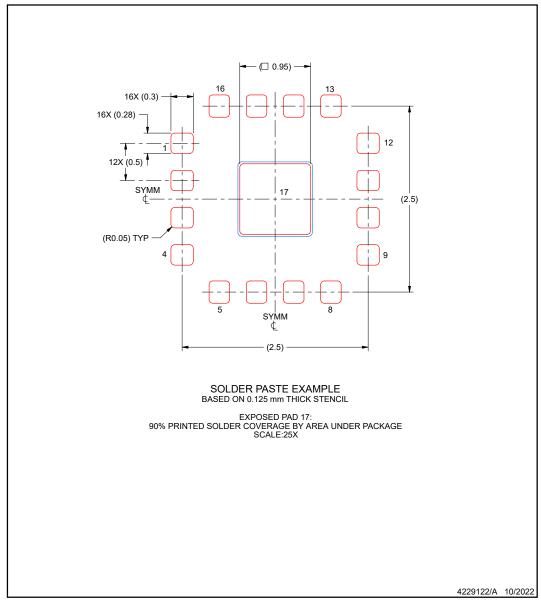

#### パッケージ情報

| 部品番号      | パッケージ (1)     | パッケージ・サイズ<br><sup>(2)</sup> |  |  |

|-----------|---------------|-----------------------------|--|--|

| LMK3H0102 | RER (TQFN、16) | 3.0mm × 3.0mm               |  |  |

- 利用可能なすべてのパッケージについては、データシートの (1) 末尾にある注文情報を参照してください。

- パッケージ・サイズ (長さ×幅) は公称値であり、該当する場 合はピンも含まれます。

概略ブロック図

·スの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確 つきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたしま

# **Table of Contents**

| 1特長                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3 概要 1 9.1 Power-Up Sequencing 9.2 Decoupling Power Supply Inputs 9.2 Decoupling Pow |                |

| 4 Pin Configuration and Functions 3 9.2 Decoupling Power Supply Inputs 4 5 Specifications 6 10 Layout 5.1 Absolute Maximum Ratings 6 10.1 Layout Guidelines 10.2 Layout Example 10.2 Layout Example 10.2 Layout Example 11.1 Device and Documentation Support 11.1 Documentation Support 11.2 ドキュメントの更新通知を受け取る方法 4 5.6 I2C Interface Specification 14 11.3 サポート・リソース 4 6 Parameter Measurement Information 16 11.4 Trademarks 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| 5 Specifications 6 5.1 Absolute Maximum Ratings 6 5.2 ESD Ratings 6 10.1 Layout Guidelines 4 10.2 Layout Example 4 10.2 Layout Example 4 10.2 Layout Example 4 10.2 Layout Example 4 11.1 Device and Documentation Support 11.1 Documentation Support 11.2 ドキュメントの更新通知を受け取る方法 4 11.3 サポート・リソース 4 11.3 サポート・リソース 4 11.4 Trademarks 4 11.4 Trademarks 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13             |

| 5.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| 5.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| 5.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| 5.5 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <del>1</del> 5 |

| 5.6 I2C Interface Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <del>1</del> 5 |

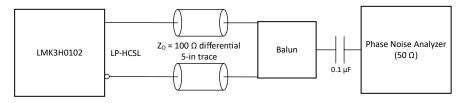

| 6 Parameter Measurement Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <del>1</del> 5 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <del>1</del> 5 |

| 0.4.0.4.1.5.4.5.4.5.4.5.4.5.4.5.4.5.4.5.4.5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <del>1</del> 5 |

| 6.1 Output Format Configurations16 11.5 静電気放電に関する注意事項4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <del>1</del> 5 |

| 7 Detailed Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <del>1</del> 5 |

| 7.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <del>1</del> 6 |

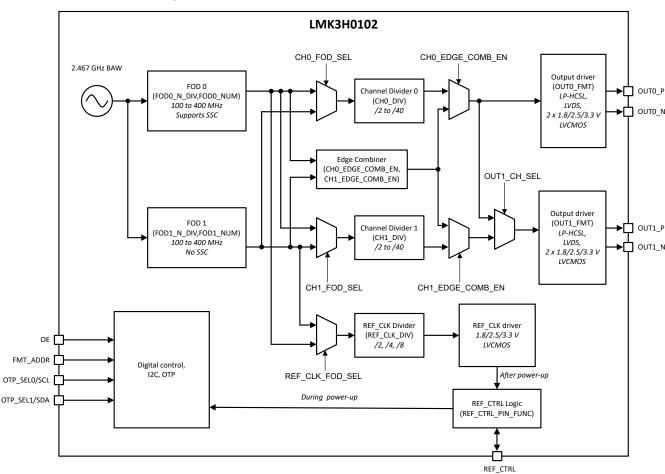

| 7.2 Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <del>1</del> 6 |

| 7.3 Feature Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56             |

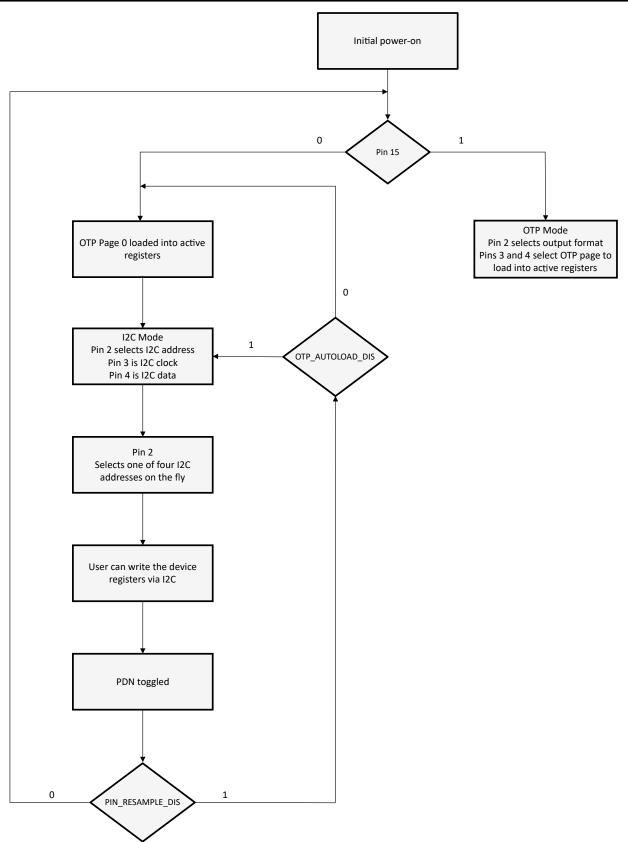

| 7.4 Device Functional Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

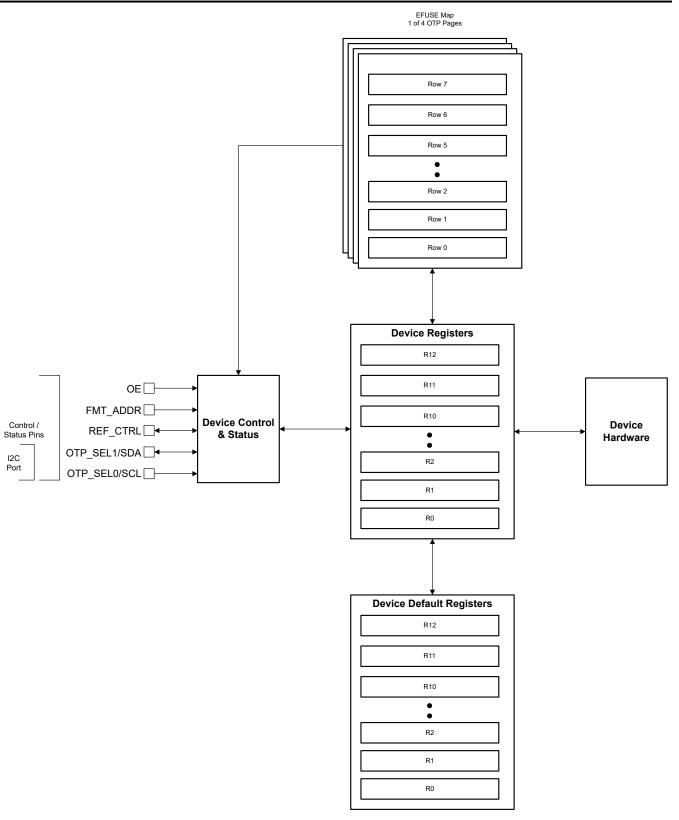

| 7.5 Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56             |

| 8 Application and Implementation34 14.1 Package Option Addendum6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30             |

| 8.1 Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31             |

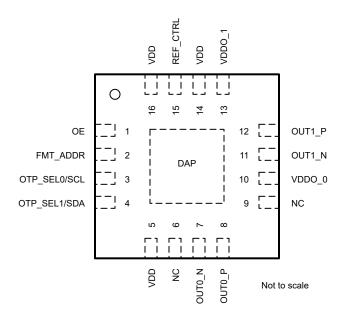

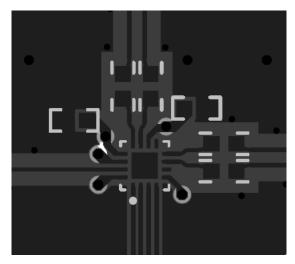

# **4 Pin Configuration and Functions**

# 図 4-1. LMK3H0102 16-Pin TQFN Top View

表 4-1. Pin Functions

| PIN                           |        | TYPE(1) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-------------------------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                          | NO.    | ITPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| OUT0_P, OUT0_N                | 8, 7   | 0       | Clock output 0. Supports LP-HCSL (85 Ω or 100 Ω), LVDS or 1.8-V/2.5-V/3.3-V LVCMOS.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| OUT1_P, OUT1_N                | 12, 11 | 0       | Clock output 1. Supports LP-HCSL (85 $\Omega$ or 100 $\Omega$ ), LVDS or 1.8-V/2.5-V/3.3-V LVCMOS.                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| REF_CTRL<br>(REF_CLK)         | 15     | I/O     | Multifunctional pin. At power up, the state of this pin is latched to select the functionality of Pin 2, Pin 3 and Pin 4. Pull low or leave floating for I2C mode or high for OTP mode prior to power-up. After power-up, this pin can be programmed as an additional LVCMOS output (REF_CLK), active-high CLK_READY signal (default), or disabled.  See REF_CTRL Operation for more details. This pin has an 880-kΩ internal pulldown resistor. |  |  |  |  |

| OE                            | 1      | I       | Global Output Enable. Active low. 2-state logic input pin. This pin has a 75-kΩ internal pulldown resistor. See Output Enable for more details.  Low/Floating: OUT0 and OUT1 enabled  High: OUT0 and OUT1 disabled                                                                                                                                                                                                                               |  |  |  |  |

| FMT_ADDR                      | 2      | I       | Multifunctional pin. Functionality is determined by REF_CTRL (pin 15) at power up. See OTP Mode and I2C Mode for more details. This pin has an 880-kΩ internal pulldown resistor.  I2C Mode: This pin selects the I2C address.  OTP Mode: This pin sets the output format.                                                                                                                                                                       |  |  |  |  |

| OTP_SEL0/SCL,<br>OTP_SEL1/SDA | 3, 4   | I, I/O  | Multifunctional pin. Functionality is determined by REF_CTRL (pin 15) at power up. See OTP Mode and I2C Mode for details. These pins have 880-kΩ internal pulldown resistors.  I2C Mode: These pins are the I2C clock and data connections.  OTP Mode: These pins select the OTP page.                                                                                                                                                           |  |  |  |  |

# 表 4-1. Pin Functions (続き)

| PIN            |        | TYPE(1) | DESCRIPTION                                                                                                                                                                                            |  |  |

|----------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME           | NO.    | ITPE    | DESCRIPTION                                                                                                                                                                                            |  |  |

| VDD            |        |         | 8-V, 2.5-V or 3.3-V device power supply. A 0.1-μF capacitor must be placed as close to ach of the pins as possible.                                                                                    |  |  |

| VDDO_0, VDDO_1 | 10, 13 | Р       | 1.8-V, 2.5-V or 3.3-V OUT0 and OUT1 power supply. If VDD is 1.8 V or 2.5 V, the VDDO pins must be the same voltage as VDD. A 0.1-µF capacitor must be placed as close to each of the pins as possible. |  |  |

| NC             | 6, 9   | N/A     | No connect. Pins can be connected to GND, VDD, or otherwise tied to any potential within the Supply Voltage range stated in the <i>Absolute Maximum Ratings</i> .                                      |  |  |

| DAP            | 17     | G       | GND                                                                                                                                                                                                    |  |  |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

# 表 4-2. BLOT

| NAME          | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT0_N        | 7   | 0                   | Clock output 0. Supports LP-HCSL (85 $\Omega$ or 100 $\Omega$ ), LVDS or 1.8-V/2.5-V/3.3-V LVCMOS.                                                                                                                                                                                                                                                                                                                                               |

| OUT0_P        | 8   | 0                   | Clock output 0. Supports LP-HCSL (85 $\Omega$ or 100 $\Omega$ ), LVDS or 1.8-V/2.5-V/3.3-V LVCMOS.                                                                                                                                                                                                                                                                                                                                               |

| OUT1_N        | 11  | 0                   | Clock output 1. Supports LP-HCSL (85 $\Omega$ or 100 $\Omega$ ), LVDS or 1.8-V/2.5-V/3.3-V LVCMOS.                                                                                                                                                                                                                                                                                                                                               |

| OUT1_P        | 12  | 0                   | Clock output 1. Supports LP-HCSL (85 $\Omega$ or 100 $\Omega$ ), LVDS or 1.8-V/2.5-V/3.3-V LVCMOS.                                                                                                                                                                                                                                                                                                                                               |

| REF_CTRL      | 15  | I/O                 | Multifunctional pin. At power up, the state of this pin is latched to select the functionality of Pin 2, Pin 3 and Pin 4. Pull low or leave floating for I2C mode or high for OTP mode prior to power-up. After power-up, this pin can be programmed as an additional LVCMOS output (REF_CLK), active-high CLK_READY signal (default), or disabled.  See REF_CTRL Operation for more details. This pin has an 880-kΩ internal pulldown resistor. |

| OE            | 1   | I                   | Global Output Enable. Active low. 2-state logic input pin. This pin has a 75-kΩ internal pulldown resistor. See Output Enable for more details.  Low/Floating: OUT0 and OUT1 enabled  High: OUT0 and OUT1 disabled                                                                                                                                                                                                                               |

| FMT_ADDR      | 2   | ı                   | Multifunctional pin. Functionality is determined by REF_CTRL (pin 15) at power up. See  OTP Mode and I <sup>2</sup> C Mode for more details.  This pin has a 75-kΩ internal pulldown resistor.  I2C Mode: This pin selects the I2C address.  OTP Mode: This pin sets the output format.                                                                                                                                                          |

| OTP_SEL0/SCL, | 3   | ı                   | Multifunctional pin. Functionality is determined by REF_CTRL (pin 15) at power up. See OTP Mode and I <sup>2</sup> C Mode for more details.  I2C Mode: These pins are the I2C clock and data connections.  OTP Mode: These pins select the OTP page.                                                                                                                                                                                             |

| OTP_SEL1/SDA  | 4   | I/O                 | Multifunctional pin. Functionality is determined by REF_CTRL (pin 15) at power up. See OTP Mode and I <sup>2</sup> C Mode for more details.  I2C Mode: These pins are the I2C clock and data connections.  OTP Mode: These pins select the OTP page.                                                                                                                                                                                             |

| VDD           | 5   | Р                   | 1.8-V, 2.5-V or 3.3-V device power supply. A 0.1-µF capacitor must be placed as close to each of the pins as possible.                                                                                                                                                                                                                                                                                                                           |

| VDD           | 14  | Р                   | 1.8-V, 2.5-V or 3.3-V device power supply. A 0.1-μF capacitor must be placed as close to each of the pins as possible.                                                                                                                                                                                                                                                                                                                           |

| VDD           | 16  | Р                   | 1.8-V, 2.5-V or 3.3-V device power supply. A 0.1-μF capacitor must be placed as close to each of the pins as possible.                                                                                                                                                                                                                                                                                                                           |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2023 Texas Instruments Incorporated

1

# 表 4-2. BLOT (続き)

| NAME   | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                     |

|--------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDO_0 | 10  | Р                   | 1.8-V, 2.5-V or 3.3-V OUT0 and OUT1 power supply. If VDD is 1.8 V or 2.5 V, the VDDO pins must be the same voltage as VDD. A $0.1$ - $\mu$ F capacitor must be placed as close to each of the pins as possible. |

| VDDO_1 | 13  | Р                   | 1.8-V, 2.5-V or 3.3-V OUT0 and OUT1 power supply. If VDD is 1.8 V or 2.5 V, the VDDO pins must be the same voltage as VDD. A 0.1- $\mu$ F capacitor must be placed as close to each of the pins as possible.    |

| NC     | 6   | N/A                 | No connect. Pins can be connected to GND, VDD, or otherwise tied to any potential within the Supply Voltage range stated in the <i>Absolute Maximum Ratings</i> .                                               |

| NC     | 9   | N/A                 | No connect. Pins can be connected to GND, VDD, or otherwise tied to any potential within the Supply Voltage range stated in the <i>Absolute Maximum Ratings</i> .                                               |

| DAP    | _   | G                   | GND                                                                                                                                                                                                             |

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                                                        | MIN  | MAX                      | UNIT |

|------------------|----------------------------------------------------------------------------------------|------|--------------------------|------|

| $V_{DD}$         | Device supply voltage                                                                  | -0.3 | 3.9                      | V    |

| $V_{DDO}$        | Output supply voltage                                                                  | -0.3 | 3.9                      | V    |

| V <sub>IN</sub>  | Logic input voltage (V <sub>DD</sub> = V <sub>DDO</sub> = -0.3 to 3.9 V)               | -0.3 | 3.9                      | V    |

| V <sub>OUT</sub> | Voltage applied to OUTx_P and OUTx_N pins (when outputs are high or low)               | -0.3 | V <sub>DDO_x</sub> + 0.3 | V    |

|                  | Voltage applied to OUTx_P and OUTx_N pins (when outputs are LVCMOS tri-state)          | -0.3 | 1.89                     | V    |

|                  | Voltage applied to OUTx_P and OUTx_N pins (when outputs are LP-HCSL or LVDS tri-state) | -0.3 | 1.5                      | V    |

| TJ               | Junction temperature                                                                   |      | 105                      | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 5.2 ESD Ratings

|                    |                         |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                  | Floatroatatio discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JS-002, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 5.3 Recommended Operating Conditions

$V_{DD} = V_{DDO} = 1.8 \text{ V}, 2.5 \text{ V or } 3.3 \text{ V} \pm 5\%, T_A = T_{A,min} \text{ to } T_{A,max}$

|                   |                                                          | MIN   | NOM | MAX   | UNIT |

|-------------------|----------------------------------------------------------|-------|-----|-------|------|

|                   |                                                          | 1.71  | 1.8 | 1.89  | V    |

| $V_{DD}$          | Device supply voltage                                    | 2.375 | 2.5 | 2.625 | V    |

|                   |                                                          | 3.135 | 3.3 | 3.465 | V    |

| V <sub>DDO</sub>  |                                                          | 1.71  | 1.8 | 1.89  | V    |

|                   | Output supply voltage                                    | 2.375 | 2.5 | 2.625 | V    |

|                   |                                                          | 3.135 | 3.3 | 3.465 | V    |

| T <sub>A</sub>    | Ambient temperature                                      | -40   |     | 85    | °C   |

| TJ                | Junction temperature                                     | -40   |     | 125   | °C   |

| t <sub>ramp</sub> | Power supply ramp time. V <sub>DD</sub> = 1.8 V          | 0.05  |     | 5     | ms   |

| t <sub>ramp</sub> | Power supply ramp time. V <sub>DD</sub> = 2.5 V or 3.3 V | 0.05  |     | 5     | ms   |

# **5.4 Thermal Information**

|                       |                                           | DEVICE            |      |

|-----------------------|-------------------------------------------|-------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>             | PKG DES (PKG FAM) | UNIT |

|                       |                                           | PINS              |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance    | TBD               | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance | TBD               | °C/W |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2023 Texas Instruments Incorporated

|                      |                                              | DEVICE            |      |

|----------------------|----------------------------------------------|-------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | PKG DES (PKG FAM) | UNIT |

|                      |                                              | PINS              |      |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | TBD               | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | TBD               | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | TBD               | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | TBD               | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 5.5 Electrical Characteristics

$V_{DD} = V_{DDO} = 1.8 \text{ V}, 2.5 \text{ V or } 3.3 \text{ V} \pm 5\%, T_A = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C}$

|                        | PARAMETER                                             | TEST CONDITIONS                                        | MIN      | TYP | MAX | UNIT |

|------------------------|-------------------------------------------------------|--------------------------------------------------------|----------|-----|-----|------|

| FREQUE                 | NCY STABILITY                                         |                                                        |          |     | '   |      |

| $\Delta f_{total}$     | Total frequency stability                             |                                                        | -25      |     | 25  | ppm  |

| Δf <sub>init</sub>     | Initial frequency stability                           | T <sub>A</sub> = 25°C                                  | -1       |     | 1   | ppm  |

| $\Delta f_{temp}$      | Frequency stability due to temperature                | Over Recommended Operating Condition, dT/dt < 10°K/min | -10      |     | 10  | ppm  |

| $\Delta f_{aging}$     | Frequency stability due to aging                      | 10 years at 25°C                                       | TBD      |     | TBD | ppm  |

| LP-HCSL                | CLOCK OUTPUT CHARACTERISTICS                          |                                                        | <u>'</u> |     |     |      |

| f <sub>out</sub>       | Output frequency                                      |                                                        | 2.5      |     | 400 | MHz  |

| V <sub>min</sub>       | Output low voltage (undershoot included)              |                                                        | -60      |     | 25  | mV   |

| V <sub>overshoot</sub> | Overshoot voltage. V <sub>max</sub> - V <sub>OH</sub> |                                                        |          |     | 150 | mV   |

|                        | Output high voltage. VDD = 2.5 V or 3.3 V             | code = 0                                               | 594      | 625 | 656 | mV   |

|                        |                                                       | code = 1                                               | 614      | 647 | 679 | mV   |

|                        |                                                       | code = 2                                               | 635      | 668 | 702 | mV   |

|                        |                                                       | code = 3                                               | 656      | 690 | 725 | mV   |

|                        |                                                       | code = 4                                               | 676      | 712 | 747 | mV   |

|                        |                                                       | code = 5                                               | 697      | 733 | 770 | mV   |

|                        |                                                       | code = 6 (default)                                     | 717      | 755 | 793 | mV   |

| V <sub>OH,2.5/3.</sub> |                                                       | code = 7                                               | 738      | 777 | 816 | mV   |

| 3                      |                                                       | code = 8                                               | 758      | 798 | 838 | mV   |

|                        |                                                       | code = 9                                               | 779      | 820 | 861 | mV   |

|                        |                                                       | code = 10                                              | 800      | 842 | 884 | mV   |

|                        |                                                       | code = 11                                              | 820      | 863 | 907 | mV   |

|                        |                                                       | code = 12                                              | 841      | 885 | 929 | mV   |

|                        |                                                       | code = 13                                              | 861      | 907 | 952 | mV   |

|                        |                                                       | code = 14                                              | 882      | 928 | 975 | mV   |

|                        |                                                       | code = 15                                              | 903      | 950 | 998 | mV   |

|                     | PARAMETER                                            | TEST CONDITIONS                                                                                                                             | MIN   | TYP | MAX   | UNIT |

|---------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

|                     |                                                      | code = 0                                                                                                                                    | 563   | 625 | 688   | mV   |

|                     |                                                      | code = 1                                                                                                                                    | 582   | 647 | 712   | mV   |

|                     |                                                      | code = 2                                                                                                                                    | 601   | 668 | 735   | mV   |

|                     |                                                      | code = 3                                                                                                                                    | 621   | 690 | 759   | mV   |

|                     | 1                                                    | code = 4                                                                                                                                    | 641   | 712 | 783   | mV   |

|                     |                                                      | code = 5                                                                                                                                    | 660   | 733 | 806   | mV   |

|                     |                                                      | code = 6 (default)                                                                                                                          | 680   | 755 | 831   | mV   |

| ,                   | Output high voltage VDD = 1.9 V                      | code = 7                                                                                                                                    | 699   | 777 | 855   | mV   |

| / <sub>OH,1.8</sub> | Output high voltage. VDD = 1.8 V                     | code = 8                                                                                                                                    | 718   | 798 | 878   | mV   |

|                     |                                                      | code = 9                                                                                                                                    | 738   | 820 | 902   | mV   |

|                     |                                                      | code = 10                                                                                                                                   | 758   | 842 | 926   | mV   |

|                     |                                                      | code = 11                                                                                                                                   | 777   | 863 | 949   | mV   |

|                     |                                                      | code = 12                                                                                                                                   | 797   | 885 | 974   | mV   |

|                     |                                                      | code = 13                                                                                                                                   | 816   | 907 | 998   | mV   |

|                     |                                                      | code = 14                                                                                                                                   | 835   | 928 | 1021  | mV   |

|                     |                                                      | code = 15                                                                                                                                   | 855   | 950 | 1045  | mV   |

| ,                   | I D I I CCI estatio differential improduce           |                                                                                                                                             | 80.75 | 85  | 91.25 | Ω    |

| <b>Z</b><br>diff    | LP-HCSL static differential impedance                |                                                                                                                                             | 95    | 100 | 105   | Ω    |

|                     |                                                      | Measured from –150 mV to +150 mV on the differential waveform, centered on the zero crossing point. OUTx_SLEW_RATE = 0 (TBD) <sup>(1)</sup> | 2.1   |     | 3.1   | V/ns |

|                     | Output slew rate (rising and falling edge)           | Measured from –150 mV to +150 mV on the differential waveform, centered on the zero crossing point. OUTx_SLEW_RATE = 0 <sup>(1)</sup>       | 2.3   |     | 3.5   | V/ns |

| dV/dt               |                                                      | Measured from –150 mV to +150 mV on the differential waveform, centered on the zero crossing point. OUTx_SLEW_RATE = 1(1)                   | 2     |     | 3.2   | V/ns |

|                     |                                                      | Measured from –150 mV to +150 mV on the differential waveform, centered on the zero crossing point. OUTx_SLEW_RATE = 2 <sup>(1)</sup>       | 1.7   |     | 2.8   | V/ns |

|                     |                                                      | Measured from –150 mV to +150 mV on the differential waveform, centered on the zero crossing point. OUTx_SLEW_RATE = 3 <sup>(1)</sup>       | 1.4   |     | 2.7   | V/ns |

| ∆dV/dt              | Rising edge rate to falling edge rate matching       | See <sup>(1)</sup>                                                                                                                          |       |     | 3     | %    |

|                     |                                                      | See <sup>(1)</sup>                                                                                                                          | 49.9  |     | 50.3  | %    |

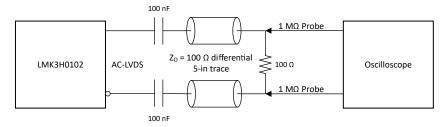

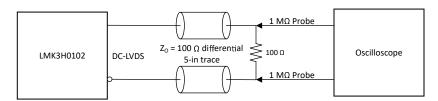

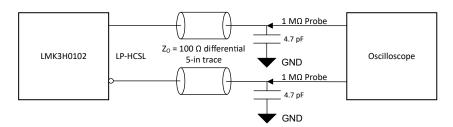

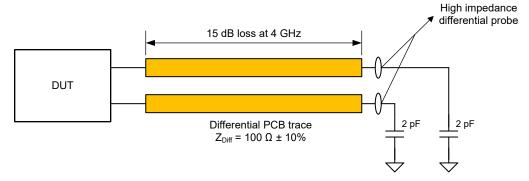

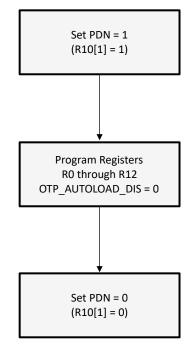

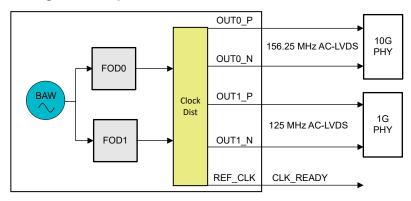

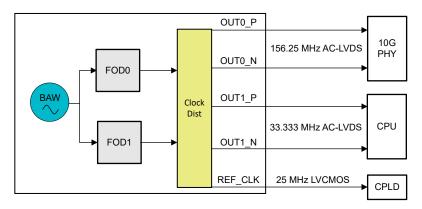

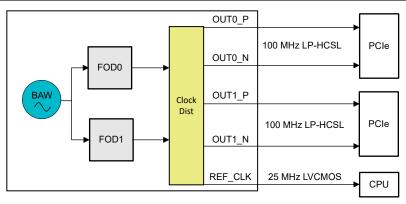

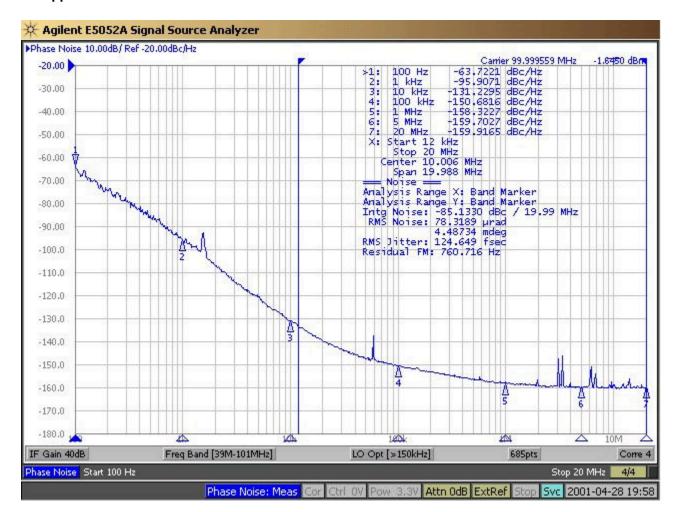

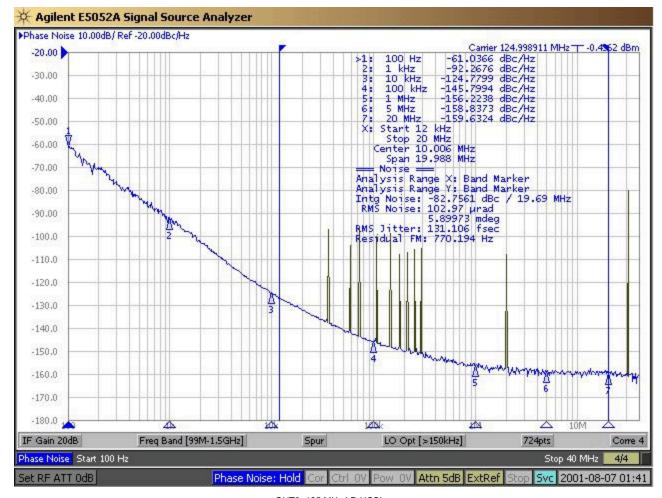

| DDC                 | Output duty cycle                                    | f <sub>out</sub> ≤ 325 MHz                                                                                                                  | 48.8  |     | 50.8  | %    |