**ADS1271**

# 24ビット広帯域A/Dコンバータ

### 特長

- 105kSPS データレート

- AC特性

帯域幅 51kHz

SN比 109dB(高分解能モード)

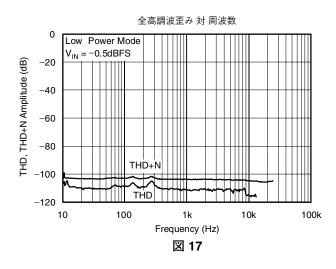

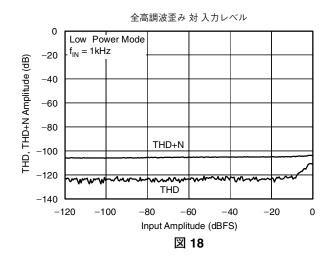

THD-105dB

DC精度

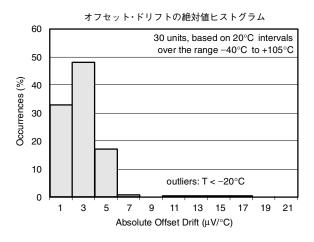

オフセット・ドリフト 1.8μV/℃ ゲイン・ドリフト 2ppm/℃

● 選択可能な動作モード

高速モード: 105kSPS データレート 高分解能モード: 109dB SN比 ローパワーモード: 35mW電力消費

- パワーダウン制御

- デジタル・フィルタ

線形位相応答

通過帯域リップル:±0.005dB 阻止帯域の減衰:100dB

● コマンドによる内部オフセット補償

- SPI<sup>TM</sup>あるいはフレーム同期のシリアル・インターフェイスが選択可能

- 2マルチチャネル・システム用途に設計 デイジー・チェイン可能なシリアル・インターフェ イス

同期が容易

- 単純なピン・ドライブ制御

- -40°Cから+105°Cで規定

- アナログ電源電圧:5V

- デジタル電源電圧:1.8Vから3.3V

### アプリケーション

- 振動/モーダル解析

- 音響

- ダイナミックひずみゲージ

- 圧力センサー

- 試験および計測

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

Tivaよび日本Tiは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

### 概要

ADS1271は24ビットのデルタ-シグマ型ADC(アナログ・トゥ・デジタル・コンバータ)であり、そのデータレートは最大105kSPSです。ADS1271は、優れたDC精度と並外れたAC特性というユニークな組み合わせを提供します。その高次のチョッパ安定型変調器は、帯域内の低ノイズとともに非常な低ドリフトを実現しています。また、実装されているデシメーション・フィルタは、変調器および信号帯域外ノイズを抑圧します。ADS1271は、使用可能な帯域幅をナイキスト周波数の最大90%まで0.005dB以下のリップルで提供します。

従来の良好なドリフト特性を提供する産業用デルタ-シグマ型ADCは、通過帯域のドループが大きいデジタルフィルタを使用しています。その結果、信号帯域幅に制限が生じており、主にDC計測用途に限られています。オーディオ・アプリケーション用の高分解能ADCはより広い使用可能な帯域幅を提供しますが、オフセットおよびドリフトの仕様がその産業用の相当品よりもはるかに劣ります。ADS1271は両方のコンバータを組み合わせて、拡張された産業温度範囲で保証する優れたACおよびDC仕様により、高精細の産業用途の計測を可能にしています。

3つの動作モードにより、変換速度、分解能、および消費電力の最適化ができます。また、SPIあるいはフレーム同期の選択可能なシリアル・インターフェイスにより、マイクロコントローラやDSPとの簡便なインターフェイスが可能です。内部オフセット補償を含めたすべての動作がピンから直接制御でき、プログラミングを要するレジスタはありません。

#### 絶対最大定格

over operating free-air temperature range unless otherwise noted (1)

|                                   | ADS1271            | UNIT |

|-----------------------------------|--------------------|------|

| AVDD to AGND                      | -0.3 to +6.0       | V    |

| DVDD to DGND                      | -0.3 to +3.6       | V    |

| AGND to DGND                      | -0.3 to +0.3       | V    |

| Innut Current                     | 100, Momentary     | mA   |

| Input Current                     | 10, Continuous     | mA   |

| Analog Input to AGND              | -0.3 to AVDD + 0.3 | V    |

| Digital Input or Output to DGND   | -0.3 to DVDD + 0.3 | V    |

| Maximum Junction Temperature      | +150               | °C   |

| Operating Temperature Range       | -40 to +105        | °C   |

| Storage Temperature Range         | -60 to +150        | °C   |

| Lead Temperature (soldering, 10s) | +300               | °C   |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

### 注文情報

最新のパッケージおよび注文に関する情報は、本データシートの巻末のパッケージ・オプション付録をご覧ください。または、弊社のウェブサイトwww.ti.comを参照願います。

### 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

#### 電気的特性

All specifications at  $T_A = -40$ °C to +105°C, AVDD = +5V, DVDD = +1.8V,  $f_{CLK} = 27$ MHz, VREFP = 2.5V, VREFN = 0V, unless otherwise noted.

|                                |                                |                                            |                         | ADS1271                 |                           |                         |

|--------------------------------|--------------------------------|--------------------------------------------|-------------------------|-------------------------|---------------------------|-------------------------|

| PARA                           | METER                          | TEST CONDITIONS                            | MIN                     | TYP                     | MAX                       | UNITS                   |

| Analog Inputs                  |                                |                                            |                         |                         |                           |                         |

| Full-scale input voltage       | (FSR)(1)                       | V <sub>IN</sub> = (AINP – AINN)            |                         | ±V <sub>REF</sub>       |                           | V                       |

| Absolute input voltage         | ,                              | AINP or AINN to AGND                       | AGND - 0.1              | 1121                    | AVDD + 0.1                | V                       |

| Common-mode input v            | oltage                         | V <sub>CM</sub> = (AINP + AINN)/2          |                         | 2.5                     |                           | V                       |

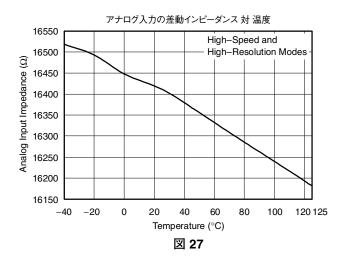

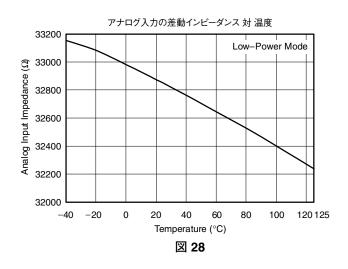

|                                | High-Speed mode                |                                            |                         | 16.4                    |                           | kΩ                      |

| Differential inputif           | High-Resolution mode           |                                            |                         | 16.4                    |                           | kΩ                      |

| impedance                      | Low-Power mode                 |                                            |                         | 32.8                    |                           | kΩ                      |

| DC Performance                 |                                |                                            |                         |                         |                           | •                       |

| Resolution                     |                                | No missing codes                           | 24                      |                         |                           | Bits                    |

|                                | High-Speed mode                |                                            |                         | 105,469                 |                           | SPS                     |

| Data rate (f <sub>DATA</sub> ) | High-Resolution mode           |                                            |                         | 52,734                  |                           | SPS                     |

|                                | Low-Power mode                 |                                            |                         | 52,734                  |                           | SPS                     |

| Integral nonlinearity (IN      | L)                             | Differential input, V <sub>CM</sub> = 2.5V |                         | ± 0.0006                | ± 0.0015                  | % of FSR <sup>(1)</sup> |

| Offeet error                   | High-Speed mode                | Without calibration                        |                         | 0.150                   | 1                         | mV                      |

| Offset error                   |                                | With calibration                           |                         | On the leve             | l of the noise            | •                       |

| Offset drift                   |                                |                                            |                         | 1.8                     |                           | μV/°C                   |

| Gain error                     |                                |                                            |                         | 0.1                     | 0.5                       | %                       |

| Gain error drift               |                                |                                            |                         | 2                       |                           | ppm/°C                  |

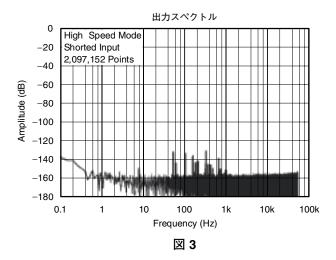

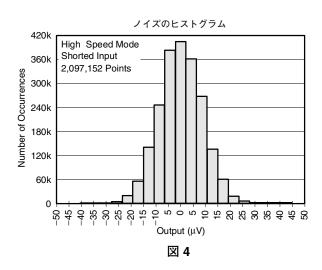

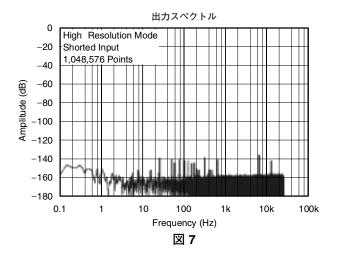

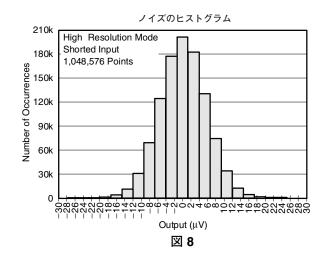

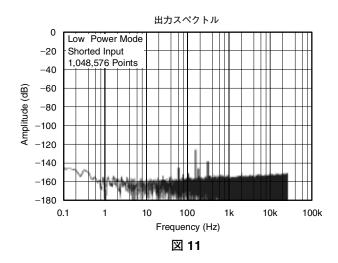

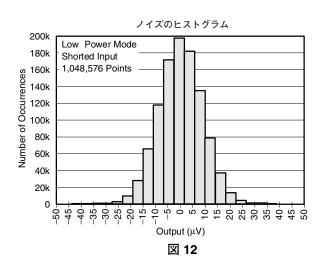

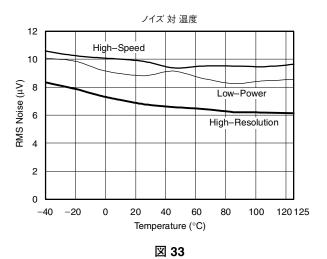

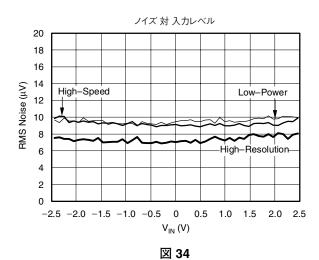

|                                | High-Speed mode                | Shorted input                              |                         | 9.0                     | 20                        | μV, rms                 |

| Noise                          | High-Resolution mode           |                                            |                         | 6.5                     |                           | μV, rms                 |

|                                | Low-Power mode                 |                                            |                         | 9.0                     |                           | μV, rms                 |

| Common-mode rejection          | n                              | f <sub>CM</sub> = 60Hz                     | 90                      | 100                     |                           | dB                      |

| Power-supply                   | AVDD                           | f 0011-                                    |                         | 80                      |                           | dB                      |

| rejection                      | DVDD                           | f = 60Hz                                   |                         | 80                      |                           | dB                      |

| AC Performance                 |                                |                                            |                         |                         |                           |                         |

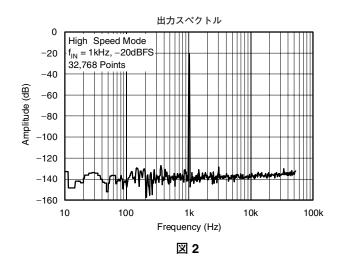

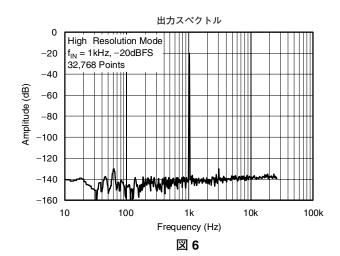

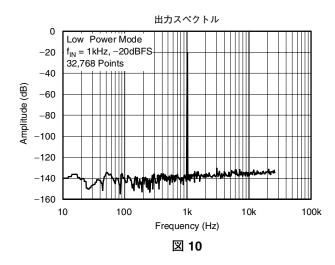

| Signal-to-noise ratio          | High-Speed mode                |                                            | 99                      | 106                     |                           | dB                      |

| (SNR) (2)                      | High-Resolution mode           |                                            |                         | 109                     |                           | dB                      |

| (unweighted)                   | Low-Power mode                 |                                            |                         | 106                     |                           | dB                      |

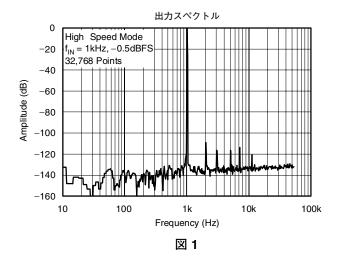

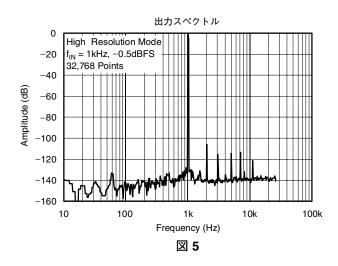

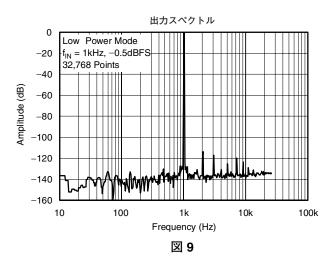

| Total harmonic distortio       | n (THD) <sup>(3)</sup>         | V <sub>IN</sub> = 1kHz, -0.5dBFS           |                         | -105                    | <b>-</b> 95               | dB                      |

| Spurious free dynamic          | range                          |                                            |                         | -108                    |                           | dB                      |

| Passband ripple                |                                |                                            |                         |                         | ±0.005                    | dB                      |

| Passband                       |                                |                                            |                         | 0.453 f <sub>DATA</sub> |                           | Hz                      |

| -3dB Bandwidth                 |                                |                                            |                         | 0.49 f <sub>DATA</sub>  |                           | Hz                      |

| Stop band attenuation          |                                |                                            | 100                     |                         |                           | dB                      |

|                                | High-Speed mode                |                                            | 0.547 f <sub>DATA</sub> |                         | 63.453 f <sub>DATA</sub>  | Hz                      |

| Stop band                      | High-Resolution mode           |                                            | 0.547 f <sub>DATA</sub> |                         | 127.453 f <sub>DATA</sub> | Hz                      |

|                                | Low-Power mode                 |                                            | 0.547 f <sub>DATA</sub> |                         | 63.453 f <sub>DATA</sub>  | Hz                      |

| Group delay                    | High-Speed and Low-Power modes |                                            |                         | 38 / f <sub>DATA</sub>  |                           | s                       |

| . ,                            | High-Resolution mode           |                                            |                         | 39 / f <sub>DATA</sub>  |                           | s                       |

| Settling time (latency)        | High-Speed and Low-Power modes | Complete settling                          |                         | 76 / f <sub>DATA</sub>  |                           | s                       |

| · 3 · - (········)/            | High-Resolution mode           | Complete settling                          |                         | 78 / f <sub>DATA</sub>  |                           | s                       |

<sup>(1)</sup> FSR = フルスケール範囲 = 2V<sub>REF</sub> (2) SN比はDCノイズ仕様のリミットで保証されます。 (3) THDは入力信号の 9 次高調波まで含みます。 (4) MODEおよびFORMATビンは除外します。 (5) SCLKに関する詳細は本文をご覧ください。

### 電気的特性(続き)

All specifications at  $T_A = -40$  °C to +105 °C, AVDD = +5 V, DVDD = +1.8 V,  $f_{CLK} = 27$ MHz, VREFP = 2.5 V, VREFN = 0V, unless otherwise noted.

|                                   |                        |                                  |                       | ADS1271 |                       |       |

|-----------------------------------|------------------------|----------------------------------|-----------------------|---------|-----------------------|-------|

| PAR                               | AMETER                 | TEST CONDITIONS                  | MIN                   | TYP     | MAX                   | UNITS |

| Voltage Reference I               | nputs                  |                                  |                       |         |                       |       |

| Reference input volta             | ge (V <sub>REF</sub> ) | V <sub>REF</sub> = VREFP – VREFN | 2.0                   | 2.5     | 2.65                  | V     |

| Negative reference in             | iput (VREFN)           |                                  | AGND - 0.1            |         | VREFP – 2.0           | V     |

| Positive reference input (VREFP)  |                        |                                  | VREFN + 2.0           |         | AVDD - 0.5            | V     |

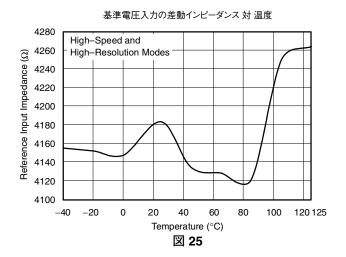

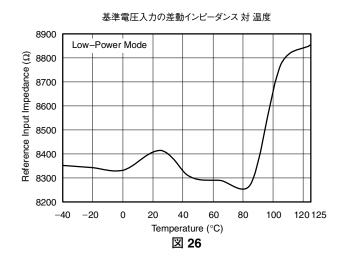

|                                   | High-Speed mode        |                                  |                       | 4.2     |                       | kΩ    |

| Reference Input impedance         | High-Resolution mode   |                                  |                       | 4.2     |                       | kΩ    |

| impedance                         | Low-Power mode         |                                  |                       | 8.4     |                       | kΩ    |

| Digital Input /Outpu              | t                      |                                  |                       |         | <u>'</u>              |       |

| VIH                               |                        |                                  | 0.7 DVDD              |         | DVDD                  | V     |

| $V_{IL}$                          |                        |                                  | DGND                  |         | 0.3 DVDD              | V     |

| VOH                               |                        | I <sub>OH</sub> = 5mA            | 0.8 DVDD              |         | DVDD                  | V     |

| V <sub>OL</sub>                   |                        | I <sub>OL</sub> = 5mA            | DGND                  |         | 0.2 DVDD              | V     |

| Input leakage <sup>(4)</sup>      |                        | 0 < VIN DIGITAL < DVDD           |                       |         | ±10                   | μΑ    |

| Master clock rate (f <sub>C</sub> | LK)                    | -                                | 0.1                   |         | 27                    | MHz   |

|                                   | SPI format             |                                  | 24 f <sub>DATA</sub>  |         | fCLK                  | MHz   |

| Serial clock rate                 |                        | High-Speed mode                  | 64 f <sub>DATA</sub>  |         | 64 f <sub>DATA</sub>  | MHz   |

| (fSCLK)(5)                        | Frame-Sync format      | High-Resolution mode             | 128 f <sub>DATA</sub> |         | 128 f <sub>DATA</sub> | MHz   |

|                                   |                        | Low-Power mode                   | 64 f <sub>DATA</sub>  |         | 64 f <sub>DATA</sub>  | MHz   |

| Power Supply                      |                        |                                  |                       |         |                       |       |

| AVDD                              |                        |                                  | 4.75                  | 5       | 5.25                  | V     |

| DVDD                              |                        |                                  | 1.65                  |         | 3.6                   | V     |

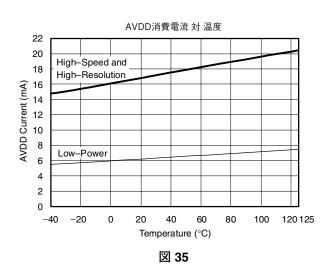

|                                   | High-Speed mode        |                                  |                       | 17      | 25                    | mA    |

|                                   | High-Resolution mode   |                                  |                       | 17      | 25                    | mA    |

| AVDD current                      | Low-Power mode         |                                  |                       | 6.3     | 9.5                   | mA    |

|                                   |                        | T > 85 °C                        |                       | 1       | 70                    | μΑ    |

|                                   | Power-Down mode        | T ≤ 85 °C                        |                       | 1       | 10                    | μΑ    |

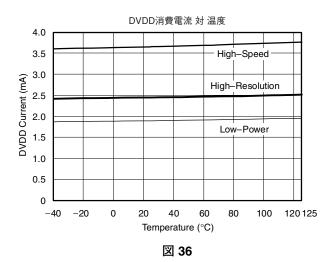

|                                   | High-Speed mode        |                                  |                       | 3.5     | 6                     | mA    |

|                                   | High-Resolution mode   | 1                                |                       | 2.5     | 5                     | mA    |

| DVDD current                      | Low-Power mode         | 1                                |                       | 1.8     | 3.5                   | mA    |

|                                   |                        | T > 85 °C, DVDD = 3.3V           |                       | 1       | 70                    | μΑ    |

|                                   | Power-Down mode        | T ≤ 85 °C, DVDD = 3.3V           |                       | 1       | 20                    | μΑ    |

|                                   | High-Speed mode        |                                  | 1                     | 92      | 136                   | mW    |

| Power dissipation                 | High-Resolution mode   |                                  |                       | 90      | 134                   | mW    |

| ·                                 | Low-Power mode         |                                  |                       | 35      | 54                    | mW    |

| Temperature Range                 | 1                      | 1                                |                       |         |                       |       |

| Specified                         |                        |                                  | -40                   |         | +105                  | °C    |

| Operating                         |                        |                                  | -40                   |         | +105                  | °C    |

| Storage                           |                        |                                  | -60                   |         | +150                  | °C    |

<sup>(1)</sup> FSR = full-scale range = 2V<sub>REF</sub>.

(2) Minimum SNR is ensured by the limit of the *DC noise* specification.

(3) THD includes the first nine harmonics of the input signal.

(4) MODE and FORMAT pins excluded.

(5) See the text for more details on SCLK.

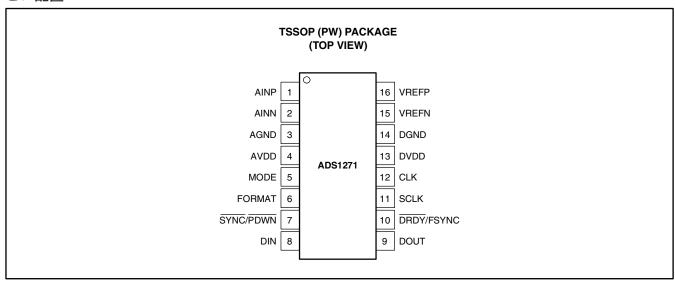

### ピン配置

#### 端子機能

| PIN        |     |                         |                                                                                                      |

|------------|-----|-------------------------|------------------------------------------------------------------------------------------------------|

| NAME       | NO. | FUNCTION                | DESCRIPTION                                                                                          |

| AINP       | 1   | Analog Input            | Positive analog input                                                                                |

| AINN       | 2   | Analog Input            | Negative analog input                                                                                |

| AGND       | 3   | Analog Input            | Analog ground                                                                                        |

| AVDD       | 4   | Analog Input            | Analog supply                                                                                        |

| MODE       | 5   | Digital Input           | MODE = 0: High-Speed mode  MODE = float: High-Resolution mode  MODE = 1: Low-Power mode              |

| FORMAT     | 6   | Digital Input           | FORMAT = 0: SPI<br>FORMAT = 1: Frame-Sync                                                            |

| SYNC/PDWN  | 7   | Digital Input           | Synchronize/Power-down input, active low                                                             |

| DIN        | 8   | Digital Input           | Data input for daisy-chain operation                                                                 |

| DOUT       | 9   | Digital Output          | Data output                                                                                          |

| DRDY/FSYNC | 10  | Digital<br>Input/Output | If FORMAT = 0 (SPI), then pin 10 = DRDY output If FORMAT = 1 (Frame-Sync), then pin 10 = FSYNC input |

| SCLK       | 11  | Digital Input           | Serial clock for data retrieval                                                                      |

| CLK        | 12  | Digital Input           | Master clock                                                                                         |

| DVDD       | 13  | Digital Input           | Digital supply                                                                                       |

| DGND       | 14  | Digital Input           | Digital ground                                                                                       |

| VREFN      | 15  | Analog Input            | Negative reference input                                                                             |

| VREFP      | 16  | Analog Input            | Positive reference input                                                                             |

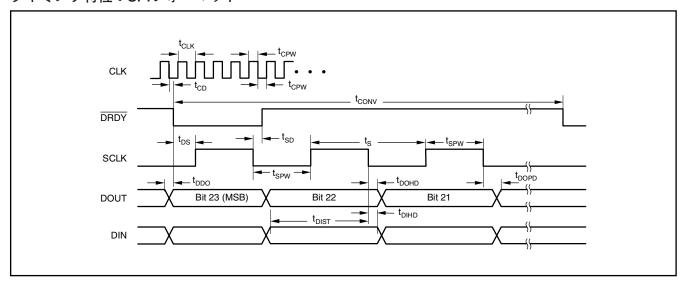

#### タイミング特性:SPIフォーマット

# タイミング仕様:SPIフォーマット For T<sub>A</sub> = -40 °C to +105°C and DVDD = 1.65V to 3.6V.

| SYMBOL                   | PARAMETER                                                          | RAMETER                                     |                  |     | MAX    | UNIT        |

|--------------------------|--------------------------------------------------------------------|---------------------------------------------|------------------|-----|--------|-------------|

| tCLK                     | CLK period (1/f <sub>CLK</sub> )                                   |                                             | 37               |     | 10,000 | ns          |

| tCPW                     | CLK positive or negative puls                                      | e width                                     | 15               |     |        | ns          |

|                          |                                                                    | High-Speed mode                             |                  | 256 |        | CLK periods |

| tCONV                    | Conversion period (1/f <sub>DATA</sub> )                           | High-Resolution mode                        |                  | 512 |        | CLK periods |

|                          |                                                                    | Low-Power mode                              |                  | 512 |        | CLK periods |

| t <sub>CD</sub> (1)      | Falling edge of CLK to falling edge of DRDY                        |                                             |                  | 8   |        | ns          |

| t <sub>DS</sub> (1)      | Falling edge of DRDY to rising edge of first SCLK to retrieve data |                                             | 5                |     |        | ns          |

| t <sub>DDO</sub> (1)     | Valid DOUT to falling edge of DRDY                                 |                                             | 0                |     |        | ns          |

| t <sub>SD</sub> (1)      | Falling edge of SCLK to rising                                     | Falling edge of SCLK to rising edge of DRDY |                  | 8   |        | ns          |

| tS <sup>(2)</sup>        | SCLK period                                                        |                                             | <sup>t</sup> CLK |     |        | ns          |

| tSPW                     | SCLK positive or negative pu                                       | lse width                                   | 12               |     |        | ns          |

| t <sub>DOHD</sub> (1)(3) | SCLK falling edge to old DOUT invalid (hold time)                  |                                             | 5                |     |        | ns          |

| t <sub>DOPD</sub> (1)    | SCLK falling edge to new DOUT valid (propagation delay)            |                                             |                  |     | 12     | ns          |

| <sup>t</sup> DIST        | New DIN valid to falling edge of SCLK (setup time)                 |                                             | 6                |     |        | ns          |

| tDIHD(3)                 | Old DIN valid to falling edge                                      | of SCLK (hold time)                         | 6                |     |        | ns          |

<sup>(1)</sup> およびDOUTの負荷=20pF

<sup>(2)</sup> 最適特性を得るために、f<sub>SCLK</sub>/f<sub>CLK</sub> を1, 1/2, 1/4, 1/8などの比に限定します。

(3) t<sub>DOHD</sub>(DOUTホールドタイム) およびt<sub>DIHD</sub>(DINホールドタイム) は、逆の最悪条件(デジタル電源電圧および周囲温度)下で指定されています。

DOUTをDINに直接に接続した等しい条件下では、タイミング余裕が4nSになります。

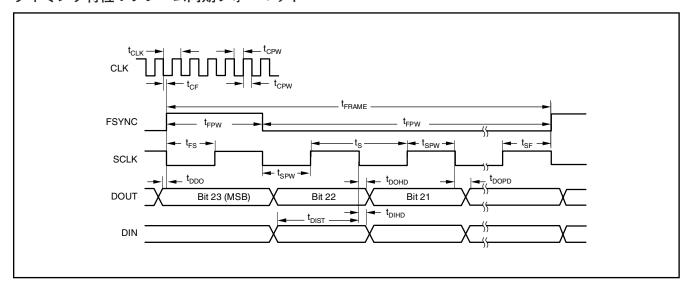

#### タイミング特性:フレーム同期フォーマット

#### タイミング仕様:フレーム同期フォーマット

for  $T_A = -40$ °C to +105°C and DVDD = 1.65V to 3.6V.

| SYMBOL               | PARAMETER                                               |                                                   | MIN                    | TYP                       | MAX                   | UNIT           |

|----------------------|---------------------------------------------------------|---------------------------------------------------|------------------------|---------------------------|-----------------------|----------------|

| tCLK                 | CLK period (1/f <sub>CLK</sub> )                        |                                                   | 37                     |                           | 10,000                | ns             |

| tCPW                 | CLK positive or negative pu                             | ulse width                                        | 15                     |                           |                       | ns             |

| tCF                  | Falling edge of CLK to falling                          | ng edge of SCLK                                   | -0.35 t <sub>CLK</sub> |                           | 0.35 t <sub>CLK</sub> | ns             |

|                      |                                                         | High-Speed mode                                   |                        | 256                       |                       | CLK periods    |

| tFRAME               | Frame period (1/f <sub>DATA</sub> )                     | High-Resolution mode                              |                        | 256 or 512 <sup>(1)</sup> |                       | CLK periods    |

|                      |                                                         | Low-Power mode                                    |                        | 256 or 512 <sup>(1)</sup> |                       | CLK periods    |

| tFPW                 | FSYNC positive or negative pulse width                  |                                                   | 1                      |                           |                       | SCLK periods   |

| t <sub>FS</sub>      | Rising edge of FSYNC to rising edge of SCLK             |                                                   | 5                      |                           |                       | ns             |

| tSF                  | Rising edge of SCLK to rising edge of FSYNC             |                                                   | 5                      |                           |                       | ns             |

|                      | 2011/                                                   | High-Speed mode                                   |                        | τFRAME/64                 |                       | τFRAME periods |

| ts                   | SCLK period (SCLK must be continuously running)         | High-Resolution mode                              |                        | τFRAME/128                |                       | τFRAME periods |

|                      | be continuously running)                                | Low-Power mode                                    |                        | τFRAME/64                 |                       | τFRAME periods |

| tSPW                 | SCLK positive or negative                               | oulse width                                       | 0.4tSCLK               |                           | 0.6t <sub>SCLK</sub>  | ns             |

| tDOHD(2)(3)          | SCLK falling edge to old Do                             | SCLK falling edge to old DOUT invalid (hold time) |                        |                           |                       | ns             |

| tDOPD(2)             | SCLK falling edge to new DOUT valid (propagation delay) |                                                   |                        |                           | 12                    | ns             |

| t <sub>DDO</sub> (2) | Valid DOUT to falling edge of FSYNC                     |                                                   | 0                      |                           |                       | ns             |

| tDIST                | New DIN valid to falling edo                            | ge of SCLK (setup time)                           | 6                      |                           |                       | ns             |

| tDIHD(3)             | Old DIN valid to falling edge                           | e of SCLK (hold time)                             | 6                      |                           |                       | ns             |

<sup>(1)</sup> ADS1271は自動的にいずれかのフレーム周期を検出します。

<sup>(2)</sup> DOUTの負荷 = 20pF

(3) t<sub>DOHD</sub> (DOUTホールドタイム) およびt<sub>DIHD</sub> (DINホールドタイム) は、逆の最悪条件 (デジタル電源電圧および周囲温度) 下で指定されています。 DOUTをDINに直接に接続した等しい条件下では、タイミング余裕が4nSになります。

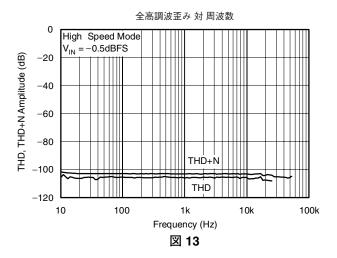

$T_A = 25^{\circ}C$ , AVDD = 5V, DVDD = 1.8V,  $f_{CLK} = 27MHz$ , VREFP = 2.5V, VREFN = 0V, unless otherwise noted.

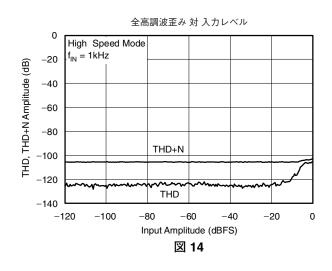

$T_A = 25$ °C, AVDD = 5V, DVDD = 1.8V,  $f_{CLK} = 27$ MHz, VREFP = 2.5V, VREFN = 0V, unless otherwise noted.

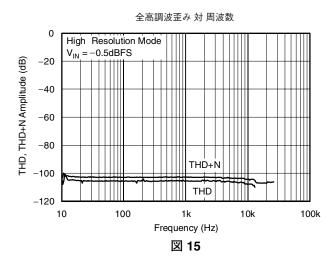

$T_A = 25^{\circ}C$ , AVDD = 5V, DVDD = 1.8V,  $f_{CLK} = 27MHz$ , VREFP = 2.5V, VREFN = 0V, unless otherwise noted.

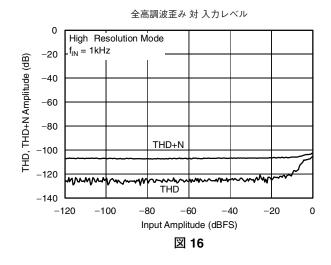

$T_A = 25$ °C, AVDD = 5V, DVDD = 1.8V,  $f_{CLK} = 27$ MHz, VREFP = 2.5V, VREFN = 0V, unless otherwise noted.

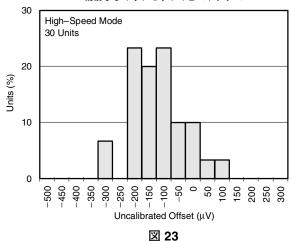

#### 補償なしのオフセットのヒストグラム

-6.0 -5.5 -5.0 \_3.5 \_3.0 \_3.0

Gain Drift (ppm/°C)

図 20

- 1.5 - 1.5 - 0.5 - 0.5

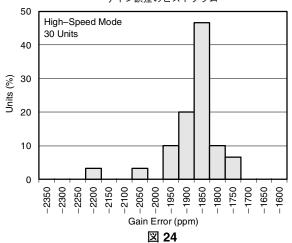

#### ゲイン誤差のヒストグラム

$T_A = 25^{\circ}C$ , AVDD = 5V, DVDD = 1.8V,  $f_{CLK} = 27MHz$ , VREFP = 2.5V, VREFN = 0V, unless otherwise noted.

$T_A = 25$ °C, AVDD = 5V, DVDD = 1.8V,  $f_{CLK} = 27$ MHz, VREFP = 2.5V, VREFN = 0V, unless otherwise noted.

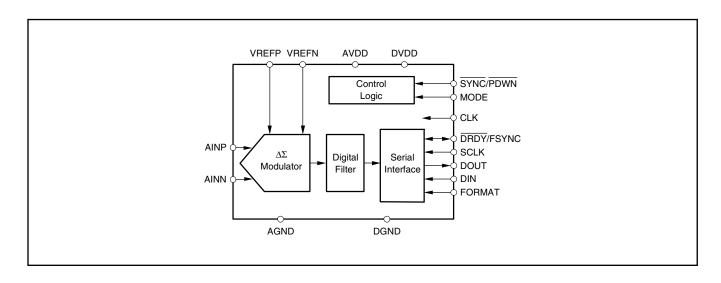

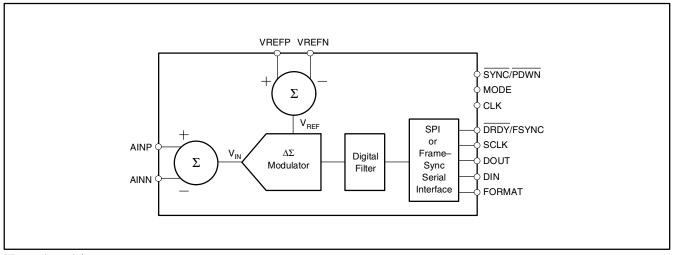

#### 概 観

ADS1271は24ビットのデルタ-シグマ型ADCであり、抜群のDC精度と優れたAC特性の組み合わせを提供します。図37にADS1271のブロック・ダイアグラムを示します。ADS1271コンバータは、先進の6次チョッパ安定型デルタ-シグマ変調器と、それに続く低リップルの線形位相FIRフィルタから構成されます。変調器は差動入力信号 $V_{IN}=(AINP-AINN)$ を差動基準電圧 $V_{REF}=(VREFP-VREFN)$ に対して計測します。デジタル・フィルタは変調器信号を受け取り、低ノイズのデジタル出力を供給します。また、変換速度、分解能、および消費電力間のトレードオフを実現するために、ADS1271は高速、高分解能、および

低消費電力の3動作モードをサポートしています。その各モードの特性を表1に要約します。高速モードではデータレートが105kSPSであり、高分解能モードではSN比 = 109dB、および低消費電力モードでは消費電力がわずか35mWです。

ADS1271は単に適切なIOピンで設定するようになっており、プログラミングを要するレジスタがありません。データは、SPIとフレーム同期の両フォーマットをサポートするシリアル・インターフェイスで取り出されます。また、ADS1271にはデイジー・チェインが可能な出力および外部から同期できる能力があるため、マルチチャネル・システムで容易に使用することができます。

図 37. ブロック図

| MODE            | DATA RATE (SPS) | PASSBAND (Hz) | SNR (dB) | NOISE (μV <sub>RMS</sub> ) | POWER (mW) |

|-----------------|-----------------|---------------|----------|----------------------------|------------|

| High-Speed      | 105,469         | 47,777        | 106      | 9.0                        | 92         |

| High-Resolution | 52,734          | 23,889        | 109      | 6.5                        | 90         |

| Low-Power       | 52,734          | 23,889        | 106      | 9.0                        | 35         |

表 1. 動作モード特性の要約

#### アナログ入力(AINP, AINN)

ADS1271は差動入力信号 $V_{IN}$  = (AINP-AINN) を差動基準電圧  $V_{REF}$  = ( $V_{REFP-VREFN}$ ) に対して計測します。差動入力の測定可能な正の最大値は+ $V_{REF}$ であり、そのデジタル出力コードは正の最大値である7FFFFFhになります。同様に、差動入力の測定可能な負の最大値は- $V_{REF}$ であり、そのデジタル出力コードは負の最大値である800000hになります。

ADS1271が差動入力信号を計測しているときの、入力電圧の 絶対値もまた重要です。これは各入力 (AINP, AINN) における AGNDに対する電圧になります。この電圧の範囲は下記のよう になります。

#### 0.1V < (AINN or AINP) < A VDD +0.1V

いずれかの入力が-0.1Vを下回るか、あるいは(AVDD + 0.1V)を上回る値になると、入力におけるESD保護ダイオードがオンします。

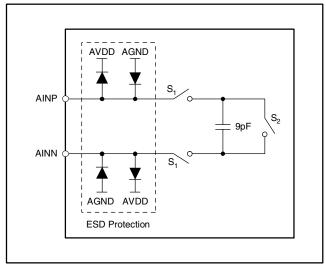

ADS1271はスイッチト・キャパシタ回路を使用して入力電圧を 測定しています。内部コンデンサは両入力で充電され、次に放 電されます。図38にこれらの回路の概念図を示します。スイッ

図 38. アナログ入力の等価回路

| MODE            | INTERFACE<br>FORMAT | fMOD                                       |

|-----------------|---------------------|--------------------------------------------|

| High-Speed      | SPI or Frame-Sync   | fCLK/4                                     |

| High-Resolution | SPI                 | fCLK/4                                     |

| nigh-Resolution | Frame-Sync          | fCLK/4 or fCLK/2                           |

| Low Dower       | SPI                 | fCLK/8                                     |

| Low-Power       | Frame-Sync          | f <sub>CLK</sub> /8 or f <sub>CLK</sub> /4 |

表 2. 異なるモードおよびフォーマットに関する変調器周波数

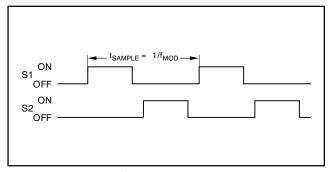

**図 39.** 図 38のS1およびS2のスイッチ·タイミング

手S2は、サンプリング用コンデンサの放電における変調器回路の全体の作用を示します。しかし、実際の回路はこれと異なります。スイッチS1およびS2のタイミングを図39に示します。サンプリング時間 ( $t_{SAMPLE}$ ) は、変調器のサンプリング周波数 ( $t_{MOD}$ ) の逆数であり、表2に示すような動作モード、インターフェイスのフォーマット、およびCLKの周波数の関数になります。フレーム同期フォーマットを高分解能あるいは低消費電力のモードで使用する場合、 $t_{MOD}$ と $t_{CLK}$ の比率はFSYNC入力で設定されるフレーム周期によって決まります。

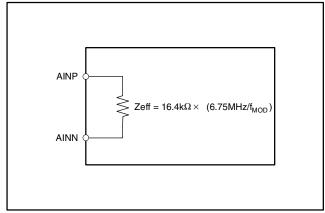

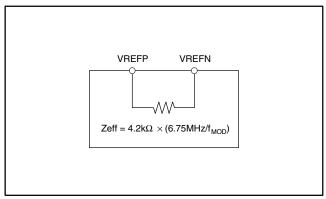

スイッチト・キャパシタ入力による平均負荷は、図40に示すような実効差動インピーダンスにモデル化できます。この実効インピーダンスはf<sub>MOD</sub>の関数になることに注意願います。

ADS1271は非常に高性能なADCです。その最適特性を得るには、適切な回路を使用してADS1271の入力をドライブすることが重要です。この推奨ドライブ回路については、『アプリケーション情報』節をご覧ください。

図 40. 実効入力インピーダンス

#### 基準電圧入力(VREFP, VREFN)

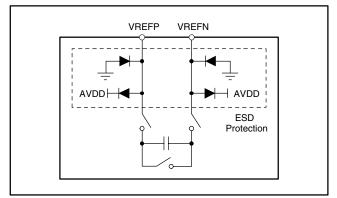

ADS1271の基準電圧は、VREFPとVREFNの2ピン間の差動電圧V<sub>REF</sub> = (VREFP-VREFN)になります。この基準電圧入力はアナログ入力と類似した構造を使用しています。その基準電圧入力の等価回路を図41に示します。アナログ入力と同様に、スイッチト・キャパシタによる負荷は図42に示す実効インピーダンスでモデル化できます。

図41において、ESDダイオードが基準電圧入力を保護します。これらのダイオードがオンしないようにするには、基準電圧ピンにかかる電圧がAGNDを0.1V以上下回らないようにします。また、同様にAVDDを0.1V以上超えないようにします。すなわち:

#### $-0.1V \le VREFN \le VREFP - 2V$

#### $VREFN + 2V \le VREFP \le AVDD - 0.5V$

適切なドライブ能力を備えた上質な基準電圧源が、ADS1271 の最高の特性を得るのに不可欠になります。基準電圧のノイズおよびドリフトは、システム全体の特性を低下させます。基準電圧源回路の例は、『アプリケーション情報』節をご覧ください。

図 41. 基準電圧入力の等価回路

図 42. 基準電圧入力の実効インピーダンス

#### クロック入力(CLK)

ADS1271には外部クロック信号をCLK入力ピンへ印加する必要があります。あらゆる高速データコンバータと同様に、最適特性には上質で低ジッタのクロックが不可欠です。したがって、水晶クロック発振器をクロック源としてお薦めします。クロック入力における過剰なリンギングは確実に除去してください。それには、47Ωの直列抵抗を使用して、クロック配線を可能なかぎり短くするのが有効です。

クロック周波数と出力データレートの比率は、動作モードとインターフェイス・フォーマットの関数になります。表3にSPIフォーマットを選択した場合の比率を示します。また、同表に代表的なCLK周波数とそれに対応するデータレートも示します。高速モードを使用する場合、変換ごとに256のCLK周期を要します。また、高分解能あるいは低消費電力のモードを選択すると、変換ごとに512のCLK周期を要します。

表4にフレーム同期フォーマットを選択した場合の比率を示します。フレーム同期フォーマットを高分解能あるいは低消費電力のモードで使用すると、の比率は256あるいは512にできます。ADS1271は、どちらの比率が使用されているか自動的に判別します。256の比率を使用すると、等しいデータレートを維持しながらCLK周波数を2分の1に低減できます。また、出力データレートはクロック周波数で調整できます。フレーム同期に関する詳細は、『シリアル・インターフェイス』節をご覧ください。

| MODE SELECTION  | fCLK/fDATA | TYPICAL f <sub>CLK</sub> (MHz) $\rightarrow$ | CORRESPONDING DATA RATE (SPS) |

|-----------------|------------|----------------------------------------------|-------------------------------|

| High-Speed      | 256        | 27 →                                         | 105,469                       |

| High-Resolution | 512        | 27 →                                         | 52,734                        |

| Low-Power       | 512        | 27 →                                         | 52,734                        |

表 3. SPIフォーマットのクロック比率

| MODE SELECTION  | fCLK/fFRAME | TYPICAL f <sub>CLK</sub> (MHz) | $\rightarrow$ | CORRESPONDING DATA RATE (SPS) |

|-----------------|-------------|--------------------------------|---------------|-------------------------------|

| High-Speed      | 256         | 27                             | $\rightarrow$ | 105,469                       |

| Link Decelution | 256         | 13.5                           | $\rightarrow$ | 52,734                        |

| High-Resolution | 512         | 27                             | $\rightarrow$ | 52,734                        |

| Law Barrer      | 256         | 13.5                           | $\rightarrow$ | 52,734                        |

| Low-Power       | 512         | 27                             | $\rightarrow$ | 52,734                        |

表 4. フレーム同期フォーマットのクロック比率

#### 動作モード選択(MODE)

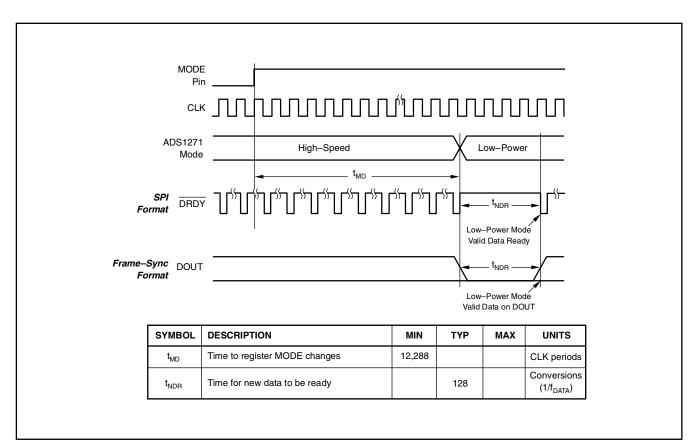

ADS1271は、高速、高分解能、および低消費電力の3動作モードをサポートします。モード選択はデジタル入力ピンMODEの状態により、表5に示すように決まります。高インピーダンスすなわちフローティング状態によって、MODEピンは3番目の状態をサポートできます。ADS1271は動作中のMODEピンの状態を常に監視し、状態の変化に対して12,288個のCLK周期後に応答します。MODEピンをフローティングにする場合、ピンにおける全容量値を100pF以下、および抵抗性負荷を10MΩ以上に保ち、適正な動作を保証するようにします。動作モードを変更すると、内部のオフセット補匠値がクリアされます。したがって、内部のオフセット補償を使用する場合、モード変更後に必ず再補償してください。

複数のADS1271を相互にデイジーチェインで使用し、高分解能モード (MODEピンをフローティング) で動作させる場合、各デバイスのMODEピンは互いに分離する必要があります。このようにすると、適正なデバイス動作が保証されます。高速および低消費電力のモードでは、MODEピンを互いに結合することができます。

| MODE PIN STATUS         | MODE SELECTION  |

|-------------------------|-----------------|

| Logic Low (DGND)        | High-Speed      |

| Floating <sup>(1)</sup> | High-Resolution |

| Logic High (DVDD)       | Low-Power       |

表 5. 動作モード選択

(1) MODEピンの負荷: C < 100pF, R > 10MΩ

SPIフォーマットを使用する場合、動作モードの変更が発生してから安定した(すなわち、適正な)データがレディになるまで、図43に示すように  $\overline{DRDY}$ はハイレベルに保たれます。

フレーム同期フォーマットでは、動作モードの変更が発生してから安定したデータがレディになるまで、図43に示すようにDOUTピンはローレベルに保たれます。したがって、データが適正であることを意味するDOUTのハイレベルへの切換わりを判別してから、デバイスからのデータを読み取ることができます。

#### フォーマット選択(FORMAT)

マイクロコントローラやDSPと容易に接続するために、ADS1271は次の2つのシリアル・インターフェイス・フォーマットをサポートしています。すなわち、SPIコンパチブルのインターフェイスとフレーム同期インターフェイスです。各フォーマットは、FORMATピンにより表6に示すように選択されます。FORMATピンは適当な電圧に直接接続することを推奨します。このピンの状態が変化したら、その後で同期操作を行って適正な動作を保証するようにします。

| FORMAT PIN STATUS | SERIAL INTERFACE FORMAT |

|-------------------|-------------------------|

| Logic Low (DGND)  | SPI                     |

| Logic High (DVDD) | Frame-Sync              |

表 6. フォーマット選択

図 43. モード切り替えタイミング

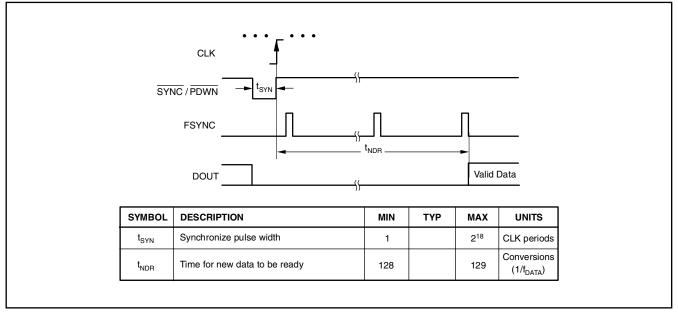

#### 同期

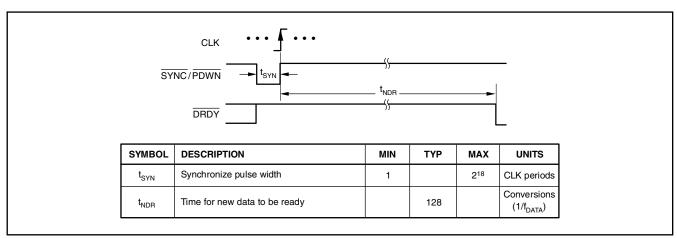

$\overline{\text{SYNC}}/\overline{\text{PDWN}}$ ピンには2つの機能があります。これにパルスを印加すると変換開始の同期をとり、 $2^{19}$ 以上のCLKサイクル ( $t_{\text{SYN}}$ )の間これをローレベルに保つと、 $\overline{\text{ADS1271}}$ をパワーダウン・モードに設定します。詳細は『パワーダウンおよびオフセット補償』の節をご覧ください。

ADS1271は、SYNC/PDWNをローレベルにして同期がとれます。このようにすると変換プロセスが停止し、デジタル・フィルタに使用される内部カウンタがリセットされます。変換プロセスを再度開始するには、SYNC/PDWNをCLKの立ち上がりエッジでハイレベルにします。同期化によってADS1271の変換を外部事象と連動させることができます。例えば、アナログ入力の外部マルチプレクサの切り換えです。また、複数のADS1271の変換を同期することもできます。

SPIフォーマットでは、図44に示すようにSYNC/PDWNがローレベルになると、すぐにDRDYがハイレベルになります。次にSYNC/PDWNがハイレベルに戻った後も、デジタル・フィルタ

がセトリングしている間は、DRDYはハイレベルのままです。 適正なデータが読み取りに対してレディになると、 はローレ ベルになります。

フレーム同期フォーマットでは、図45に示すようにSYNC/PDWNがローレベルになると、すぐにDOUTがローレベルになります。次にSYNC/PDWNがハイレベルに戻った後も、デジタル・フィルタがセトリングしている間は、DOUTはローレベルのままです。適正なデータが読み取りに対してレディになると、DOUTは適正なデータの出力を開始します。ADS1271は、SYNC/PDWNピンの状態をその立ち下がエッジで検出します。複数のADS1271を同期する場合、SCLKの立ち上がりエッジでSYNC/PDWNピンをハイレベルに設定し、すべてのADS1271が同一のSCLK周期で確実にリスタートするようにします。同期化の間は、FSYNCとSCLKを入力し続けることをお奨めします。

図 44. SPIフォーマットの同期化タイミング

図 45. フレーム同期フォーマットの同期化タイミング

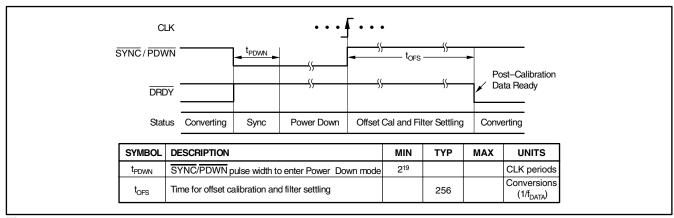

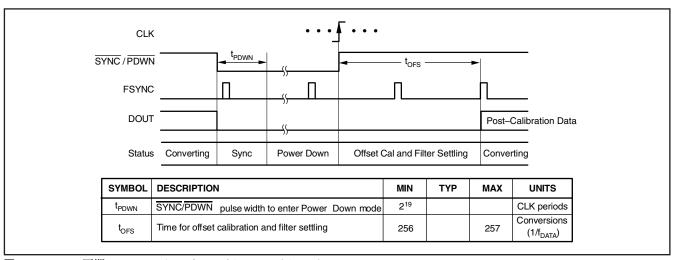

#### パワーダウンおよびオフセット補償

同期制御にくわえて、SYNC/PDWNピンはパワーダウン・モードとオフセット補償を制御する役割もします。このモードに入るには、SYNC/PDWNピンを最小2<sup>19</sup>CLK周期分だけローレベルに保ちます。パワーダウン・モードの間は、アナログとデジタルの両方の回路が完全に機能を停止します。デジタル入力は内部的にディスエーブルされるので、CLKおよびSCLKを停止する必要はありません。パワーダウン・モードを抜けるには、CLKの立ち上がりエッジでSYNC/PDWNをハイレベルに戻します。

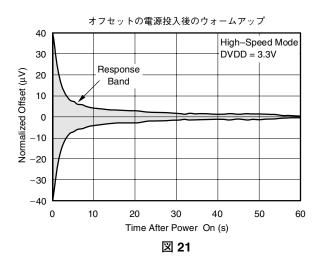

ADS1271はチョッパ安定型変調器を使用して、もとより非常な低オフセット・ドリフトを提供しています。しかし、それ以上にオフセットを最小化するため、ADS1271はパワーダウン・モードを抜ける時にオフセットの自己補償を実施しています。パワーダウンが完了すると、オフセットの自己補償が始まります。このとき、アナログ入力AINPおよびAINNが自動的に信号源から分離され、内部で互いに短絡されます。この補償の実行中は、アナログ入力に印加する信号源を操作する必要はありません。

パワーダウン・モードを抜けるときは、基準電圧を安定にしておく必要があります。さもないと、補償がうまくいきません。

オフセットの自己補償は、デバイス内部のオフセット誤差を除去するだけであり、外部起因のオフセット誤差を除去するものではありません。

注記:オフセット自己補償がなされると、その結果のオフセット 値はコンバータのノイズのピーク・トゥ・ピーク値範囲内で毎回異 なります。高速モードでは、それは一般的に178LSBになります。

オフセットの補正値は、デバイスの動作モードが変る(例えば、高速モードから高分解能モードへ)たびにクリアされます。

SPIフォーマットを使用する場合、パワーダウン・モードを抜けた後のデジタル・フィルタがセトリングする間、図46に示すようにDRDYはハイレベルのままです。

フレーム同期フォーマットを使用する場合、パワーダウン・モードを抜けた後のデジタル・フィルタがセトリングする間、図47に示すようにDOUTはローレベルのままです。

注記:パワーダウン・モードでは、ADS1271の入力をドライブしておく必要があります(入力をフローティングにしてはなりません)。また、このときADS1271は出力をあるDCレベルにドライブします。

図 46. SPIフォーマットのパワーダウンのタイミング

図 47. フレーム同期フォーマットのパワーダウンのタイミング

#### パワーアップ・シーケンス

アナログおよびデジタル電源は、いかなるアナログあるいは デジタル入力のドライブに先んじて立ち上げる必要がありま す。各電源を立ち上げる順序は任意です。各電源と基準電圧入 力が安定したら、すぐにADS1271からのデータを読み取ること ができます。

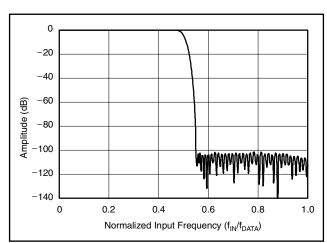

#### 周波数応答

デジタル・フィルタがデバイス全体の周波数応答を設定します。フィルタには多段FIRトポロジーを使用し、最小の通過帯域リップルかつ阻止帯域における高減衰の線形位相を提供しています。デジタル・フィルタのオーバーサンプリング・レシオ(すなわち、出力データレートに対する変調器のサンプリングの比: $f_{MOD}/f_{DATA}$ )は、表7に示すように選択された動作モードの関数になります。 $f_{MOD}$ はCLK/2あるいはCLK/4であり、動作モードによります。

#### 高速モードおよび低消費電力モード

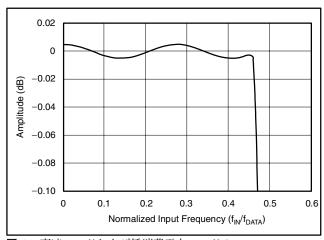

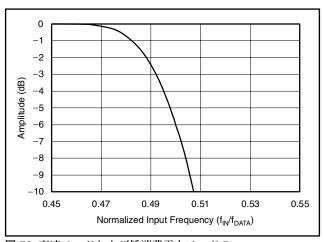

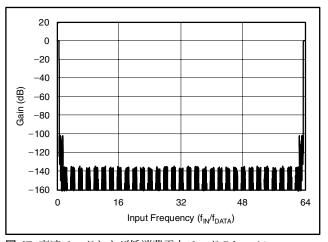

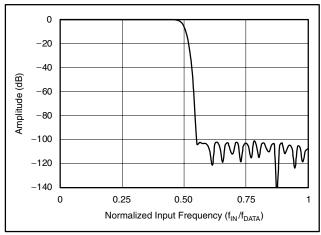

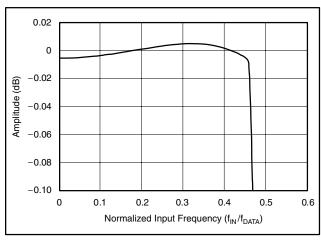

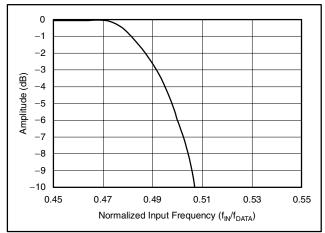

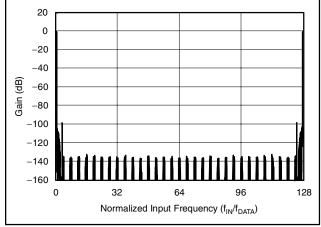

デジタル・フィルタの構成は、高速および低消費電力の両動作モードで同一であり、オーバーサンプリング・レシオは64に設定されます。図48に、高速および低消費電力の両動作モードのf<sub>DATA</sub>で正規化した周波数特性を示します。また、図49に通過帯域のリップルを示します。さらに、通過帯域から阻止帯域への遷移帯域を図50に示します。全体の周波数応答は、図51に示すように変調器周波数f<sub>MOD</sub> (64×f<sub>DATA</sub>)の倍数ごとに繰り返します。これらのイメージ周波数が信号内に存在し、かつ部的にフィルタされなければ、通過帯域へ折り返されて(すなわち、エイリアシング)誤差を発生します。しかし、阻止帯域が非常に広いので、一般に1個の単純な低次のアンチ・エイリアシング・フィルタが、帯域外ノイズを制限するためにADS1271の前で必要になるだけです。この詳細に関しては表8をご覧ください。

| MODE            | OVERSAMPLING RATIO (f <sub>MOD</sub> /f <sub>DATA</sub> ) |

|-----------------|-----------------------------------------------------------|

| High-Speed      | 64                                                        |

| High-Resolution | 128                                                       |

| Low-Power       | 64                                                        |

表 7. オーバーサンプリング・レシオ 対 動作モード

図 48. 高速モードおよび低消費電力モードの周波数応答

図 49. 高速モードおよび低消費電力モードの 通過帯域の周波数応答

図 **50.** 高速モードおよび低消費電力モードの 遷移帯域の周波数応答

**図 47.** 高速モードおよび低消費電力モードのf<sub>MOD</sub>に 対する周波数応答

#### 高分解能モード

高分解能モードのオーバーサンプリング・レシオは128です。 図52に、高分解能モードにおけるf<sub>DATA</sub>で正規化した周波数応 答を示します。また、図53に通過帯域のリップルを示し、通過 帯域から阻止帯域への遷移帯域を図54に示します。全体の周波 数応答は、図55に示すように変調器周波数 $f_{MOD}$ の倍数 (128× $f_{DATA}$ ) ごとに繰り返します。しかし、阻止帯域が非常に広いので、一般に 1 個の単純な低次のアンチ・エイリアシング・フィルタが、帯域外ノイズを制限するためにADS1271の前で必要になるだけです。この詳細に関しては表8をご覧ください。

図 52. 高分解能モードの周波数応答

図 53. 高分解能モードの通過帯域の周波数応答

図 54. 高分解能モードの遷移帯域の周波数応答

図 55. 高分解能モードの に対する周波数応答

| ANTIALIAS    | IMAGE REJECTION (dB)<br>(f_3dB at fDATA) |     |

|--------------|------------------------------------------|-----|

| FILTER ORDER | HS, LP                                   | HR  |

| 1            | 39                                       | 45  |

| 2            | 75                                       | 87  |

| 3            | 111                                      | 129 |

表 8. アンチ・エイリアシング・フィルタ次数 対 イメージ除去

#### 位相応答

ADS1271には、多段構成の線形位相デジタル・フィルタが組み込まれています。線形位相フィルタは、入力周波数に対して一定の遅延時間(一定の群遅延)になります。すなわちこれは、あらゆる時点の入力信号から同じ時点での出力データへの遅延時間が一定であり、入力信号周波数に依存しないということを意味します。マルチ・トーン信号を解析する場合、この動作により基本的に位相誤差がゼロになります。

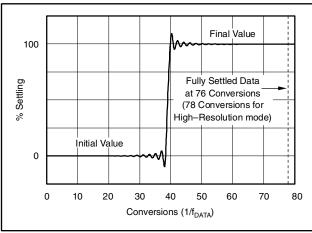

#### セトリング・タイム

周波数および位相応答と同様に、デジタル・フィルタはセトリング・タイムも決定します。図56は、アナログ入力をステップ変化させた後の、変換周期で正規化した出力のセトリング動作を示します。X軸の単位は変換周期です。アナログ入力でステップ変化が発生した後、出力データの変化が30変換周期より前では非常にわずかであることに注意願います。出力データは、高速および低消費電力モードでは76変換周期後に、高分解能モードでは78変換周期後に十分セトリングしています。

#### データ・フォーマット

ADS1271は24ビットデータを2の補数形式で出力します。正のフルスケール入力は7FFFFFhの出力コードになり、負のフルスケール入力は800000hの出力コードになります。フルスケールを超える信号の出力は、これらのコードにクリップされます。表9は、異なる入力信号に対する理想的な出力コードについての要約です。

#### シリアル・インターフェイス

ADS1271からのデータは、シリアル・インターフェイスを用いて読み取られます。マイクロコントローラやDSPとの接続を容易にするため、SPIおよびフレーム同期の2種類のインターフェイス・フォーマットが用意されています。FORMATピンで、どちらかのインターフェイスを選択します。両方のインターフェ

図 56. 全動作モードのセトリング・タイム

イスに対して同じピン (SCLK, DRDY/FSYNC, DOUT, およびDIN) を使用しますが、これらのピンの機能は選択されたインターフェイスによって各々異なります。

#### SPIシリアル・インターフェイス

SPI互換のフォーマットは、単純なリード・オンリーのインターフェイスです。読み取りに対するデータ・レディはDRDY出力によって表示され、データはSCLKの立ち下がりエッジでMSBから先にシフトアウトされます。このインターフェイスは、複数のADS1271を使用する場合、DIN入力を使ってデイジー・チェイン接続ができます。この詳細は『デイジー・チェイン』節をご覧ください。

#### SCLK(SPIフォーマット)

シリアル・クロック(SCLK)はシュミットトリガー入力特性を備え、その立ち下がりエッジでDOUTピンにデータをシフトアウトします。また、DINピンをデイジー・チェインに使用する場合も、SCLKの立ち下がりエッジでDINピンのデータをシフトインします。ADS1271はSCLKの立ち下がりエッジでデータを出力し、ユーザはSCLKの立ち上がりエッジでこのデータを入力します。SCLK入力にヒステリシスがあるとは言え、SCLK波形は極力クリーンにして、グリッチによるデータの誤シフトを防止することを推奨します。SCLKはデータ読み取り後にローレベルに保つ必要があります。また、SCLKはCLKと等しい周波数まで上げることができます。さらに、変換中はSCLKを自走あるいはストップ・クロック動作のいずれにもできます。コンバータの変換特性を最大化するために、CLKに対するSCLKの比を下記のようにします。

$$SCLK = \frac{CLK}{2^N}$$

$(N = 0, 1, 2...)$

| INPUT SIGNAL V <sub>IN</sub><br>(AINP – AINN)            | IDEAL OUTPUT CODE(1) |

|----------------------------------------------------------|----------------------|

| ≥ +V <sub>REF</sub>                                      | 7FFFFh               |

| +V <sub>REF</sub><br>2 <sup>23</sup> - 1                 | 000001h              |

| 0                                                        | 000000h              |

| -V <sub>REF</sub><br>2 <sup>23</sup> - 1                 | FFFFFh               |

| $\leq -V_{REF} \left( \frac{2^{23}}{2^{23} - 1} \right)$ | 800000h              |

表 9. 入力信号 対 理想出力コード

(1) ノイズ、INL、オフセット、およびゲイン誤差の影響を除外します。

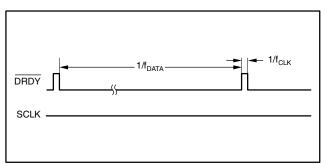

#### **DRDY / FSYNC**

SPIフォーマットでは、本ピンは $\overline{DRDY}$ 出力として機能します。読み取りに対してデータがレディならば本ピンはローレベルになり、それに続く最初のSCLKの立ち下がりエッジでハイレベルに戻ります。データが読み取られない(すなわち、SCLKがローレベルを維持)場合、次の変換データがレディになる直前に  $\overline{DRDY}$ は図57のようにハイレベルを出力します。 $\overline{DRDY}$ がローレベルになる1CLK周期前に、新しいデータはADS1271内でロードされます。したがって、重ね書きを避けるために、全データはこのタイミングまでにシフトアウトされなければなりません。

図 57. 読み取り無し時の $\overline{DRDY}$ タイミング

#### **DOUT**

変換データはDOUTピンにシフトアウトされます。 DRDYがローレベルになると、MSBのデータがDOUTピンで有効になります。それに続く下位ビットは、SCLKの各立ち下がりエッジでシフトアウトされます。デイジー・チェインをする場合、DINを使用してシフトインされたデータは、24ビットのデータすべてがシフトアウトされた後にDOUTに出力されます。

#### DIN

複数のADS1271を相互にデイジー・チェインする場合に、本 入力は使用されます。最初のADS1271のDOUTピンを次のデバ イスのDINピンに接続します。本ピンは、SPIあるいはフレー ム同期のいずれのフォーマットにも使用できます。データは SCLKの立ち下がりエッジでシフトインされます。また、 ADS1271を単体で使用する場合は、DINをローレベルに接続し ます。この詳細は『デイジー・チェイン』節をご覧ください。

#### フレーム同期シリアル・インターフェイス

フレーム同期フォーマットは、オーディオADCによく使用されるインターフェイスに類似しています。すなわち、スレーブ形式で動作します。したがってユーザは、フレーム信号のFSYNC(ステレオ・オーディオADCのレフト/ライト・クロックに類似)、およびシリアル・クロックのSCLK(オーディオADCのビット・クロックに類似)を供給する必要があります。データはMSBファーストすなわちレフト・ジャスティファイド(左揃え)で出力されます。フレーム同期を使用する場合、CLK、

FSYNC,およびSCLK入力は以下のサブ節で述べるように、それぞれ同期していなければなりません。

#### SCLK(フレーム同期フォーマット)

シリアル・クロック (SCLK) はシュミットトリガー入力特性を備え、その立ち下がりエッジでDOUTピンにデータをシフトアウトします。また、DINピンをデイジー・チェインに使用する場合も、SCLKの立ち下がりエッジでDINピンのデータをシフトインします。SCLK入力にヒステリシスがあるとは言え、SCLK波形は極力クリーンにして、グリッチによるデータの誤シフトを防止することを推奨します。フレーム同期フォーマットを使用する場合、SCLKは連続的に供給する必要があります。SCLKを停止すると、データの読み取りを誤ります。フレーム同期フォーマットは、表10に示すモードで決まる特定の関係をSCLKとFSYNCの間に要します。

| MODE            | REQUIRED SCLK PERIOD    |

|-----------------|-------------------------|

| High-Speed      | τFRAME/64               |

| High-Resolution | τ <sub>FRAME</sub> /128 |

| Low-Power       | τFRAME/64               |

表 10. フレーム同期フォーマット使用時のSCLK周期

#### **DRDY / FSYNC**

フレーム同期フォーマットでは、本ピンはFSYNC入力として使用されます。フレーム同期入力 (FSYNC) はフレーム周期を設定します。必要なFSYNC周期を表11に示します。高速モードのFSYNC周期は、256のCLK周期である必要があります。高分解能および低消費電力の両モードについては、256あるいは512CLK周期のFSYNC周期が可能です。ADS1271は、どちらが使用されているか自動的に判別します。FSYNC周期が適切な値でなければ、データの読み取りを誤ります。FSYNCはSCLKの立ち下がりエッジと同期をとることを推奨します。

| MODE            | REQUIRED FSYNC PERIOD  |

|-----------------|------------------------|

| High-Speed      | 256 CLK Periods        |

| High-Resolution | 256 or 512 CLK periods |

| Low-Power       | 256 or 512 CLK periods |

表 11. FSYNC周期

#### **DOUT**

変換データはDOUTピンにシフトアウトされます。FSYNC がハイレベルになる前のSCLKの立ち上がりエッジで、MSBのデータがDOUTピンで有効になります。それに続く下位ビットは、SCLKの各立ち下がりエッジでシフトアウトされます。デイジー・チェインをする場合、DINを使用してシフトインされたデータは、24ビットのデータすべてがシフトアウトされた後にDOUTに出力されます。

#### DIN

複数のADS1271を相互にデイジー・チェインする場合に、本入力は使用されます。本ピンは、SPIあるいはフレーム同期のいずれのフォーマットにも使用できます。データはSCLKの立ち下がりエッジでシフトインされます。また、ADS1271を単体で使用する場合は、DINをローレベルに接続します。この詳細は『デイジー・チェイン』節をご覧ください。

#### デイジー・チェイン

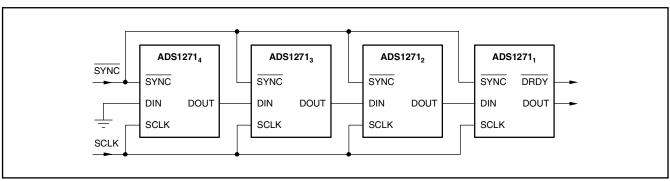

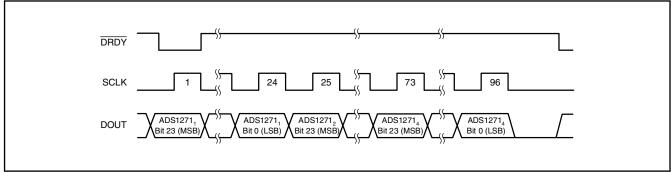

複数のADS1271を相互にデイジー・チェインして、シリアル・インターフェイスを単純化できます。それには、ひとつのADS1271のDOUTを次のADS1271のDINに接続します。最初のDOUTは出力データを提供し、チェイン内の最後のDINはグランドに接続します。また、デイジー・チェイン内のすべてのADS1271に共通のSCLKを使用します。図58に、4個のADS1271を用いたデイジー・チェインの例を示します。図59に、SPIフォーマット時の読み取りのタイミング図を示します。すべてのデータをシフトアウトするには96のSCLKが必要です。

SPIフォーマットでは、すべての $\overline{\text{SYNC}}/\overline{\text{PDWN}}$ 入力を相互に接続して、すべての $\overline{\text{ADS1271}}$ の同期をとることを推奨します。複数の $\overline{\text{ADS1271}}$ をこのように構成すると、 $\overline{\text{1}}$ デバイスの $\overline{\text{DRDY}}$ 出力を監視するだけで済みます。

フレーム同期フォーマットでは、すべてのADS1271は FSYNCおよびSCLKにより同期して動作します。しかし、同一の $f_{CLK}$ サイクル (CLK) に確実に同期するように、すべての  $\overline{SYNC}/\overline{PDWN}$ 入力を互いに接続することを推奨します。

ADS1271は $f_{CLK}$ の立ち下がりエッジで $\overline{SYNC}/\overline{PDWN}$ ピンをクロックします。したがって、正確な同期をとるために $f_{CLK}$ の立

ち上がりエッジでSYNC/PDWNピンを遷移させます。

DOUTおよびDINはともにSCLKの立ち下がりエッジでシフトされるので、DOUTの伝播遅延時間がDINのセットアップ・タイムになります。したがって、SCLKのスキューを最小にしてタイミング違反を防止します。デイジー・チェイン時のMODEピンの使用については、『モード選択』の節をご覧ください。

デイジー・チェイン時のSPIフォーマットは、SCLK周波数の設定がより自由なため最大の柔軟性を提供します。デイジー・チェインにできるADS1271の最大数は、24ビットすべてのデータを読み取るのに必要な時間  $(24\times1/f_{DATA})$  で変換時間  $(1/f_{CLK})$ を割って求まります。

ここで、以下の例について考察します。

$f_{CLK} = 27MHz$

mode = High-Resolution (52,734SPS)

format = SPI

$f_{SCLK} = 27MHz$

このデイジー・チェインの最大長は、

$27MHz/(24 \times 52,734SPS) = 21.3$

これを切り捨てると、デイジー·チェインにできるADS1271 の最大数として21が得られます。

デイジー・チェインはフレーム同期フォーマットでも可能です。しかし、デイジー・チェインにできるADS1271の最大数は、SPIフォーマットの使用時よりも少なくなります。なぜなら、フレーム周期とSCLK周期の比率が、表10に示すように固定だからです。上記の数値を使用すると、ADS1271の最大数は高速および低消費電力のモードで2、高分解能モードで5になります。

図 58. 複数ADS1271のSPIフォーマット時のデイジー・チェイン接続例

**図 59.** 図 58(SPIフォーマット)の例のタイミング図

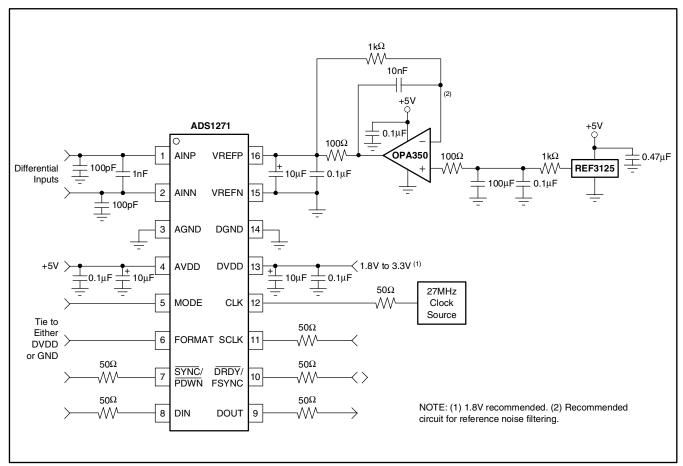

### アプリケーション情報

ADS1271から仕様の特性を引き出すには、以下のレイアウトおよび部品のガイドラインを考慮する必要があります。

- 1. 電源:ADS1271は動作するのにDVDDおよびAVDDの2電源が必要です。DVDDの許容電圧範囲は1.65Vから3.6Vであり、AVDDは4.75Vから5.25Vに制限されています。最高の特性はDVDD = 1.8Vのときに得られます。両方の電源について、10μFのタンタル・コンデンサを使用し、さらに0.1μFのセラミック・コンデンサでバイパスし、それらをデバイスの電源ピンの直近に配置します。あるいは、10μFのセラミック・コンデンサを単体で使用することもできます。電源はノイズを相対的に少なくし、電圧スパイクを発生するデバイス(例えば、リレー、LEDディスプレイ・ドライバなど)と電源を共有しないようにします。スイッチング電源を使用する場合は、電圧リップルを低く(< 2mV)します。電源シーケンスは任意の順序にできます。

- 2. グランド・プレーン:AGNDおよびDGNDの両方を接続した 単一のグランド・プレーンを使用できます。デジタルとアナ ログを分離したグランドを使用する場合は、両グランドを コンバータのところで互いに接続します。

- 3. デジタル入力: ADS1271へのデジタル入力は、50Ωの直列抵抗で信号源終端することを推奨します。この抵抗はデジタル信号源(発信器、ロジック・ゲート、DSPなど)のドライブ端に接近して配置します。このようにすると、ADC特性の劣化につながるデジタル信号ラインのリンギングを低減するのに役立ちます。

- 4. アナログ/デジタル回路:アナログ回路(入力バッファ、基準電圧源)およびそれに関連する配線をデジタル回路(DSP、マイクロコントローラ、ロジック)から離して配置します。また、デジタル信号配線とアナログ信号配線の交差を排除し、ノイズ結合およびクロストークを低減します。

- 5. 基準電圧入力:基準電圧入力のREFPおよびREFN間に、最低  $10\mu F$ のタンタル・コンデンサと $0.1\mu F$ のセラミック・コンデンサを接続することを推奨します。基準電圧入力は低インピーダンスの信号源でドライブします。最高特性を得るために、基準電圧の広帯域ノイズは $3\mu V_{RMS}$ 以下にします。この値以上のノイズがある基準電圧については、外付けの基準電圧用フィルタが必要になります。

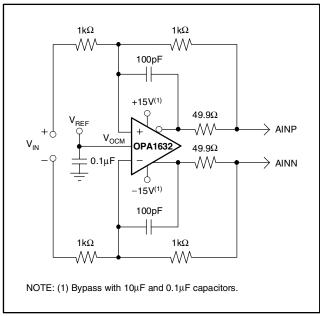

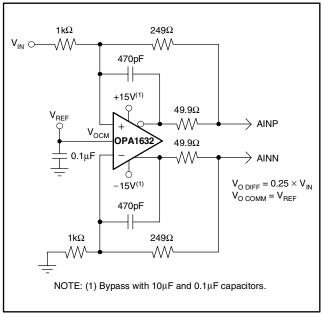

- 6. アナログ入力:アナログ入力は差動的にドライブし、仕様の特性を実現する必要があります。正確な差動ドライバあるいはトランス(ACアプリケーション)が、この目的に使用できます。アナログ入力配線(AINP, AINN)はペアにして、バッファからコンバータへ短く直行するように引き回し、デジタル信号配線から遠ざけます。

1nFから10nFのコンデンサをAINPおよびAINNのアナログ 入力ピン間に直接接続します。低誘電率のコンデンサ (COG やフィルムタイプのような)を使用し、低THDを確保します。また、各アナログ入力ピンとグランド間にもコンデンサをそれぞれ接続します。これらは差動コンデンサ (AINPとAINN間に接続したもの)の容量値の1/10より大きくせず (一般に100pF)、AC同相特性を保ちます。

7. 部品配置:電源、アナログ入力、および基準電圧入力用のバイパス・コンデンサは、できるだけデバイス・ピンの近くに配置します。これは特に小容量のセラミック・コンデンサについて重要です。表面実装タイプの部品を使用し、高インダクタンスのリード部品を排除することを推奨します。

図60から図62は、ADS1271に使用できる基本的な接続および インターフェイスを示します。

図 60. 基本的な接続図

図 61. 基本的な差動信号インターフェイス

図 62. 基本的なシングルエンド信号インターフェイス

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。丁!製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。丁!製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装 すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上